## **High-Speed Board Design Rules**

# to Get Your PCB Designed Right the First Time

## **Shalom Shlomi Zigdon**

+972509771770 Whatsup / Linkedin

Shalom-shlomi-zigdon@itech-icollege.com

www.iTech-iCollege.com

#### My name is: Shalom Shlomi Zigdon

**CEO** of iTech iCollege – Board Design Academy 1981-2001 20 yrs as HW Engineer, VP Engineering, Startup CEO 2014-2018 Chairman of IEEE Symposium **Signal Integrity & EMC** Conference 2017-2018 TAC [Technical Advice Committee] member of Boston EDI CON 2002-today Hi-Speed Consultant for SI/PI/EMC + PCB Layout Lecturer and CEO at Board Design Acadmy for SIPI&EMC 1981 B.Sc. in Electronics, Technion, the Israel institute of technology. 1985 M.A in Project Management, University of Haifa, Israel 2002 C.I.D. at Silicon Valley IPC Designers Council

Shalom-Shlomi-Zigdon@iTech-iCollege.com

## 2017+2018 TAC [Technical Advisory Committee] Members:

#### Eric Bogatin Steve Sandler, Managing Director, Picotest Shalom Shlomi Zigdon, CEO & Owner, iTech iCollege Israel Bert Simonovich, Consultant & Founder LAMSIM Enterprises Inc.

Tim Boles, Technology Fellow & Director of Strategy, MACOM Syed Bokhari, Technical Manager SI & EMC, Fidus Systems, Inc. Gregory M. Bonaguide, Senior Product Line Engineer R&S USA, Inc. Diana Baxter, Director of Engineering, Peregrine Semiconductor Antonio Ciccomancini Scogna, Principal Engineer, Samsung Jay Diepenbrock, SI/RF Consultant Lewis Dove, SI Architect, Keysight Laboratories—ASIC Technology Patrick Hindle, Editor, Microwave Journal Sheena Hussaini, PhD, R&D Engineer, Nokia Henry Lau, CEO, Lexiwave Technology, Inc. Gary LeRude, Technical Editor, Microwave Journal Anil-Kumar Pandey, Principal R&D Engineer, Keysight Technologies Ray Pengelly, GaN Power Amplifier Design Consultant Granthana Rangaswamy, Senior System SI Engineer, Juniper Networks Kalyu Zhao, R&D Engineer, Synopsys Shalom-Shlomi-Zigdon@iTech-it

#### **Boston EDI CON 2017**

Shalom-Shlomi-Zigdon@iTech-iCollege.com www.Board-Design-Academy

## Committee members since 2002

#### IPC-2251 Task Group

Amit Bhardwaj, Polar Instruments (AP) Pro 141.

Dr. Eric Bogatin, Giga Test Labs

Robert Bremer, Litton Systems Inc.

Christine R. Coapman, Delphi Delco Electronics Systems

David J. Corbett, Defense Supply Center Columbus

Theodore Edwards, Dynaco Corp.

Werner Engelmaier, Engelmaier Associates, L.C.

Martyn Gaudion, Polar Instruments Limited

Michael R. Green, Lockheed Martin Space Systems Company Richard P. Hartley, C.I.D., Hartley Enterprises Phillip E. Hinton, Hinton 'PWB' Engineering David H. Hoover, Flextronics Michael Jouppi, Thermal Man, Inc. Thomas E. Kemp Rockwell Collins George T. Kotecki, Northrop Grumman Corporation Rene R. Martinez, Northrop Grumman Deepak K. Pai, C.I.D.+, General

Dynamics-Advanced Information Nicholas G. Paulter, NIST Lee W. Ritchey, Speeding Edge Mohammad Rahnavard, Xerox Corporation John Reynolds, Rogers Corporation Lowell Sherman, Defense Supply Center Columbus Ken Taylor, Polar Instruments, Inc. Daniel Welch, Arlon MED Philip R. Wellington, L-3 Communications

Shlomi Zigdon, B.Sc., C.I.D., Shlomi Zigdon Technologies Ltd.

## **USA** Activities

### EDI CON: Santa Clara 2018 + Boston EDI CON 2017

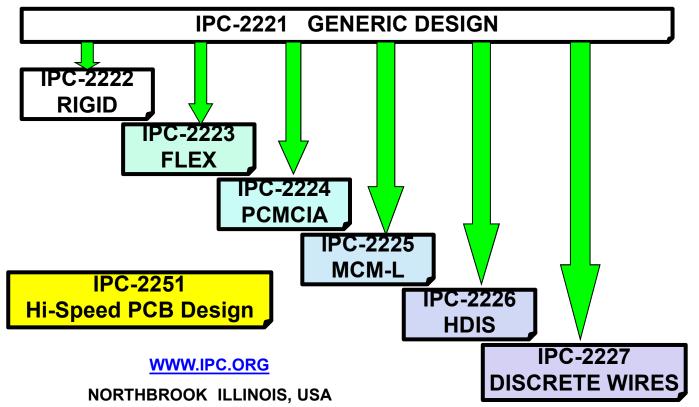

**IPC** - A committee-member of 3 **IPC Standards**:

IPC-2251 Hi-Speed Board Design for Signal Integrity

IPC-2221 PCB Design

IPC-2226 HDI- Hi Density PCBs Design.

#### **Seminars & Consultant**

5 Days Course - Intel Santa Clara 2015 +

Project PCB Design and Simulations – BD, Maryland

San Diego - PCB Layout & Simulation 2016

NYC Hilton – Hi-Speed Board Design 2017 Shalom-Shlomi-Zigdon@iTech-iCollege.com

Next USA Seminars [hopefully] :

Santa Clara January 28-31

Los Angeles April 15-18

## Agenda

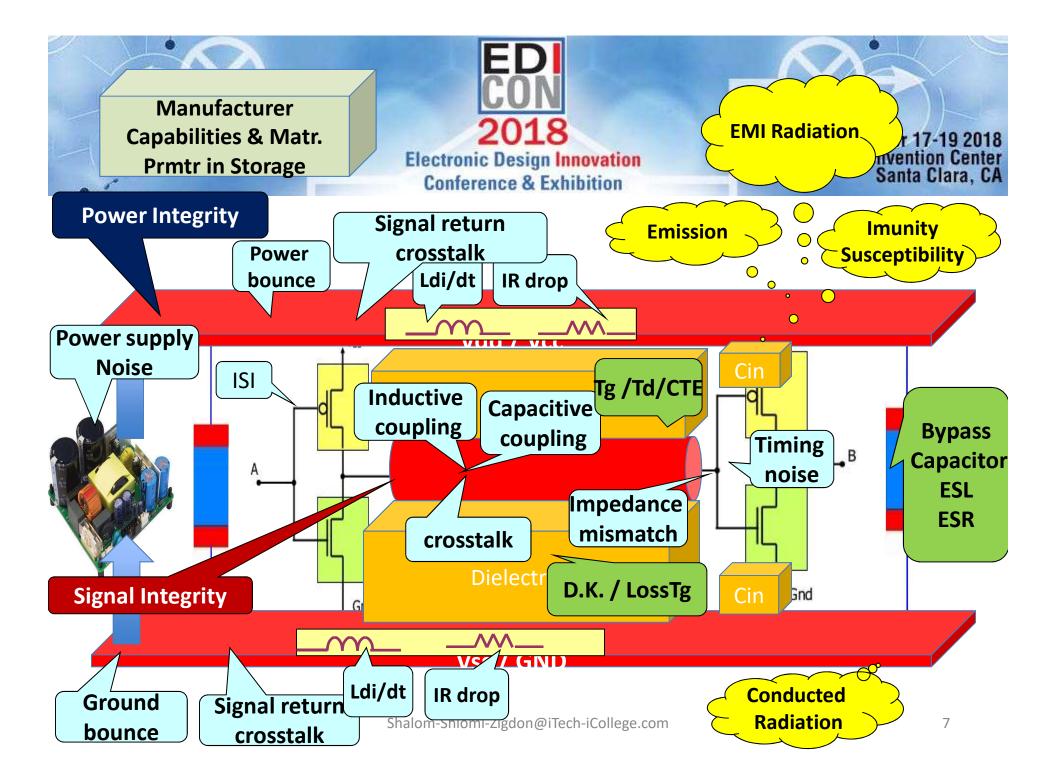

## SI/PI/EMI main problems

## What prevent us from The first time right possibility

Practical guidelines to the PCB Layout Design

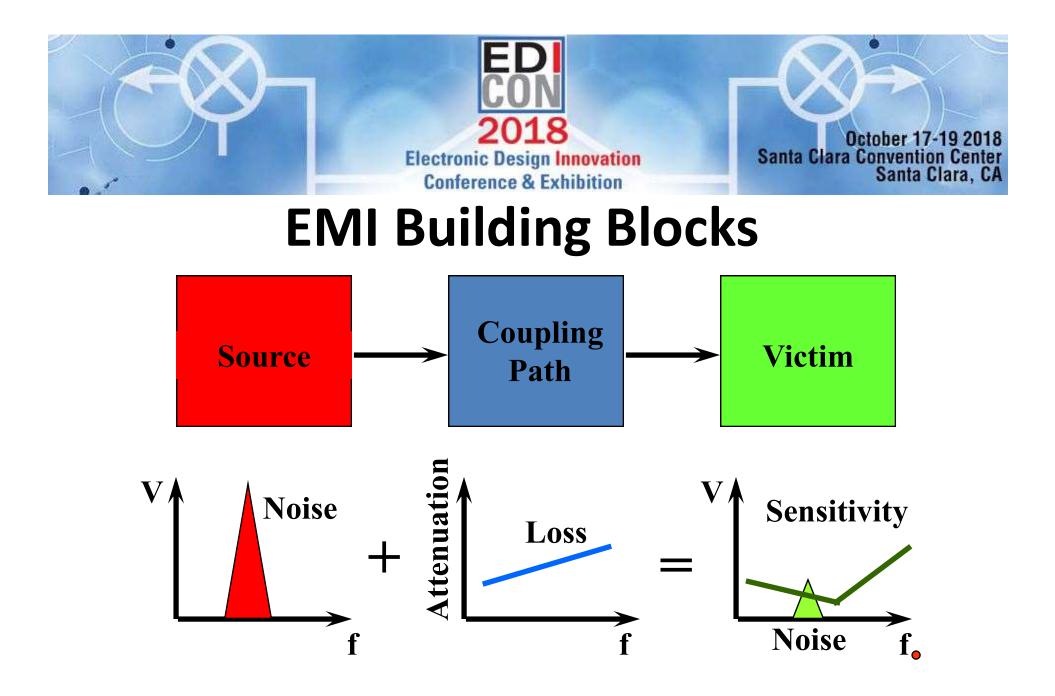

# **Definition of EMI**

# Any Electro Magnetic phenomena causing an equipment or system to malfunction .

## **Definition of EMC**

The Capability of a system to perform as designed in the intended Electro-Magnetic Environment <sup>o</sup>

#### **Electromagnetic Interference (EMI) Coupling Path**

EMI is produced by a source emitter and is detected by a susceptible victim via a coupling path

VICTIM

Sensitivity

## mechanisms:

- 1. Conduction -

- 2. Radiation -

9

- 3. Inductive Coupling -

- 4. Capacitive Coupling -

electric current

- electromagnetic field

- magnetic field

- electric field

# **Right the First Time?**

An impossible mission

# Even God did not create the world Right the First Time!!!

#### the Book of Genesis chapter 1:

floodwaters ... .... 31 re was ev <u>t</u> ence. 12 e on earth ha 13 for the earth troy both is the and the calth

Shalom-Shlomi-Zigdon@iTech-iCollege.com

October 17-19 2018 Santa Clara Convention Center Santa Clara, CA

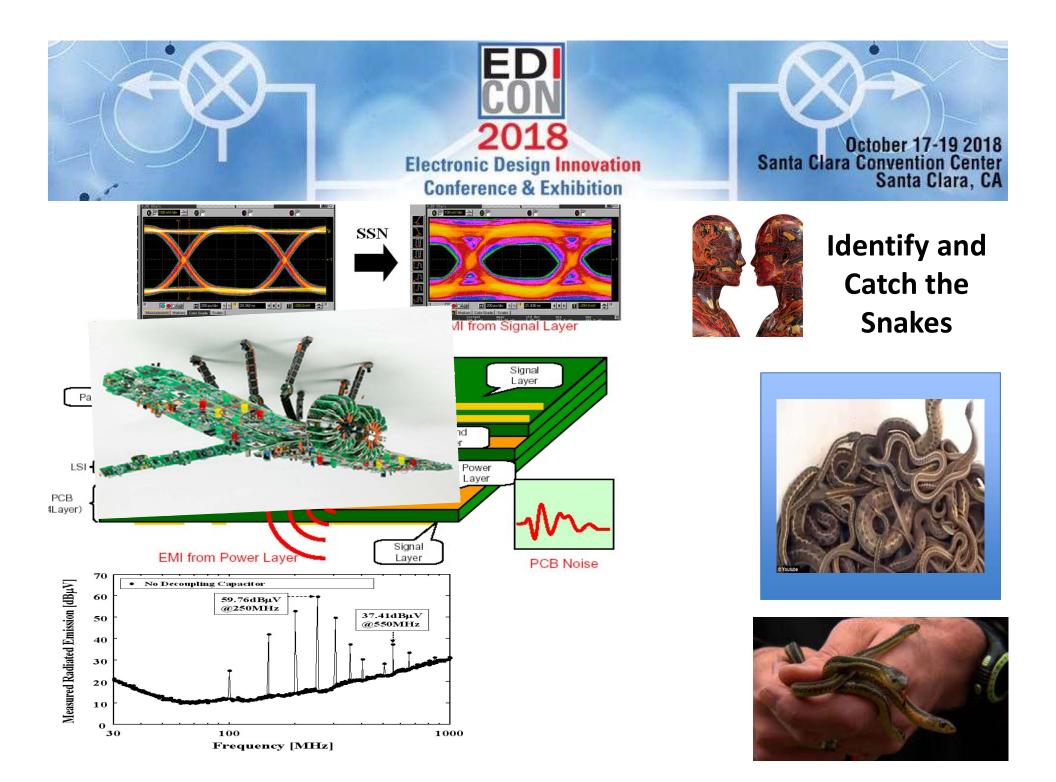

Adam & Eve where in Paradise with a Snake inside it

our Project may look like Paradise as long as it's at the Schema stage

but The PCB is full of Snakes

The Snake desired Eve

October 17-19 2018

Santa Clara, CA

Santa Clara Convention Center

#### I can understand that

Genesis:23 So the LORD God banished him from the Garden of Eden to work the ground from which he had been taken. The Copper Serpent/Snake done by Moses Cured people

## Copper Snakes can Cure Hidden Snakes in your PCB

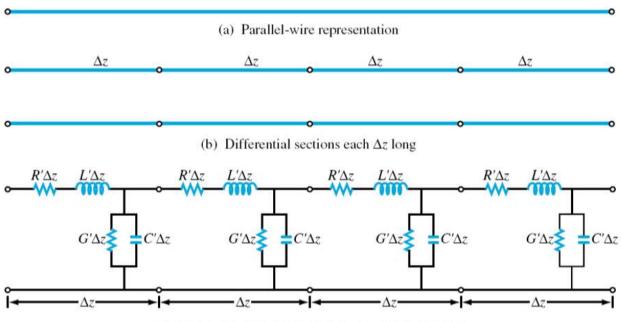

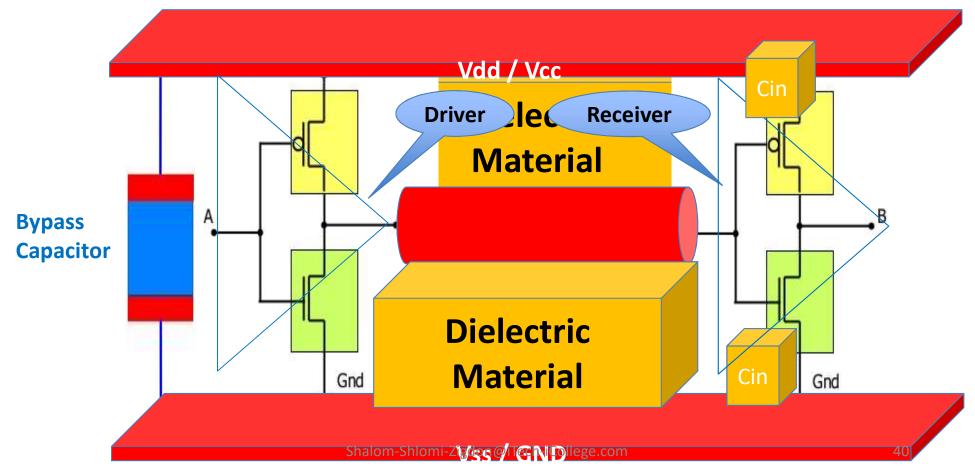

Our Premium Snake is The Return Current through the GND/PWR Planes of Copper And the Parasitic Elements of the PCB Materials

> Design it Control it

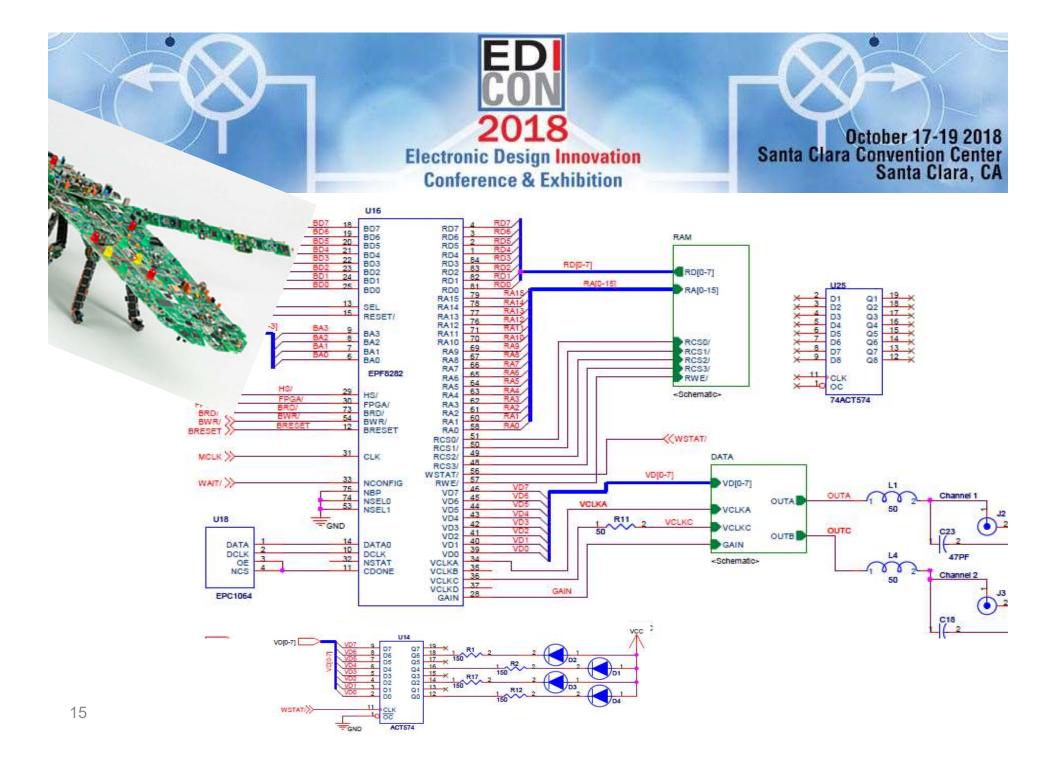

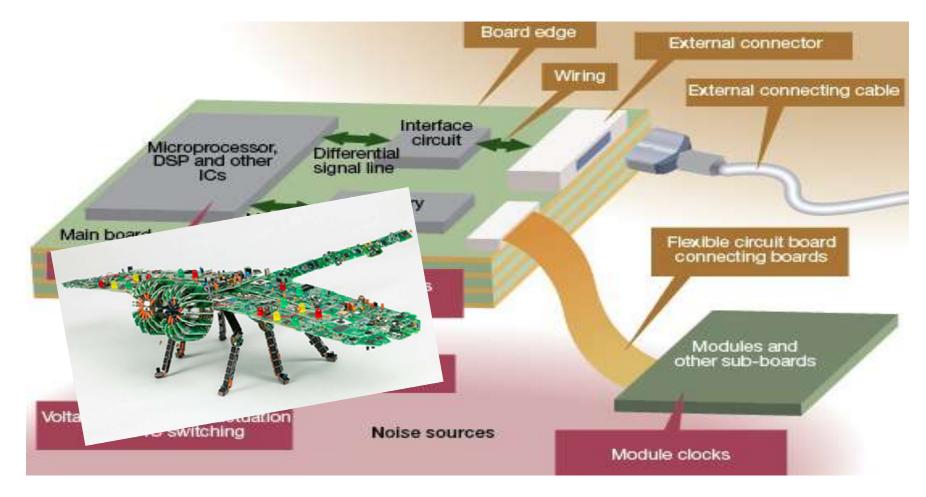

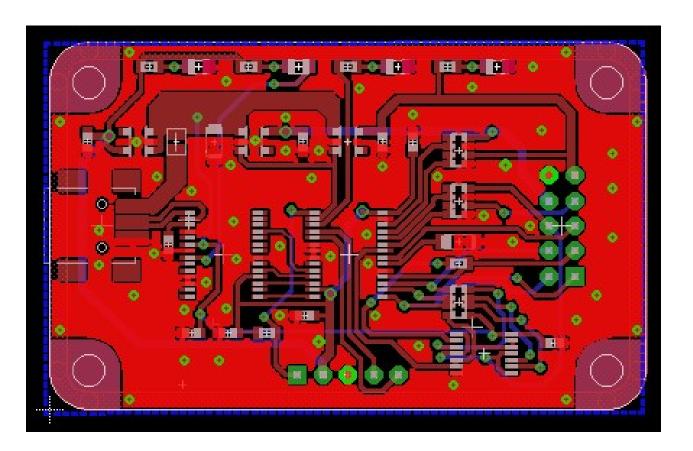

## Snakes in the real PCB

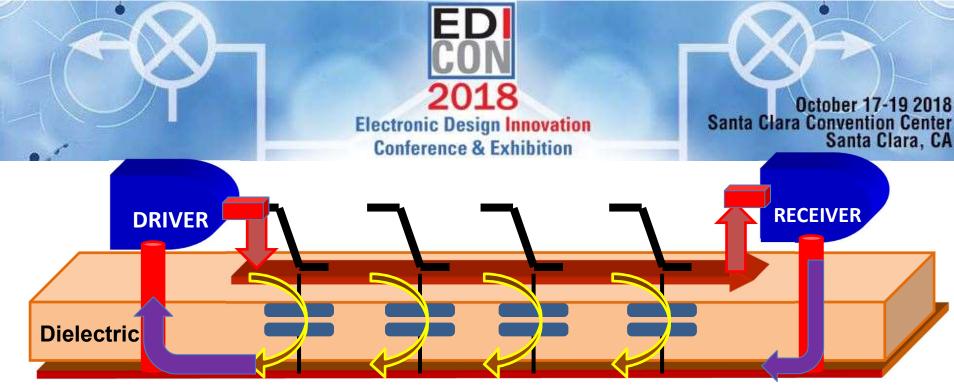

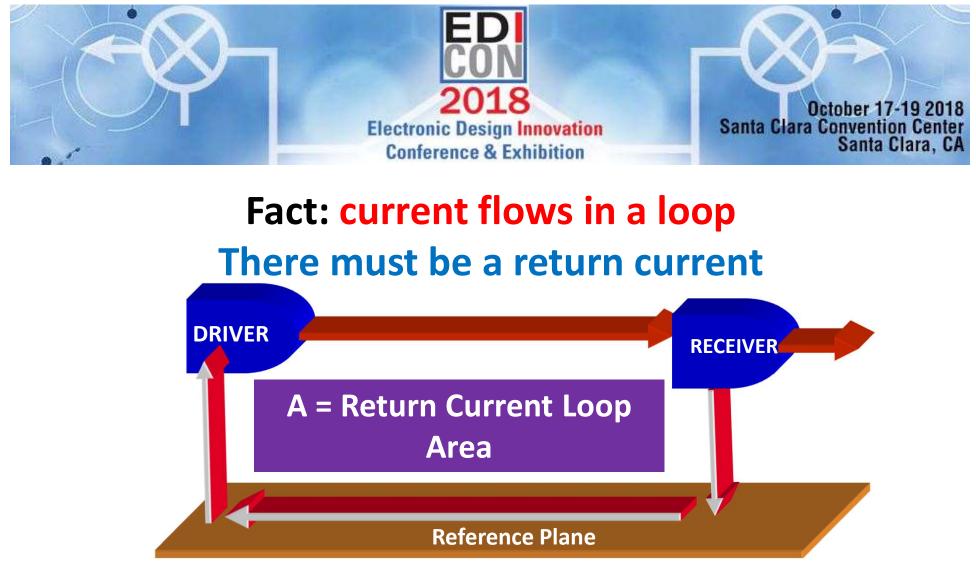

The return current path is The hidden parts of the Signal Path

Materials:

Dielectric Constant & Loss Tangent of Basic Dielectric Material Resistance & Inductance of Copper Conductors

Parasitic Capacitance between Conductors and Planes

Mutual Inductance >>>>>Crosstalk by CouplingMutual Capacitance >>>>>Crosstalk by Coupling

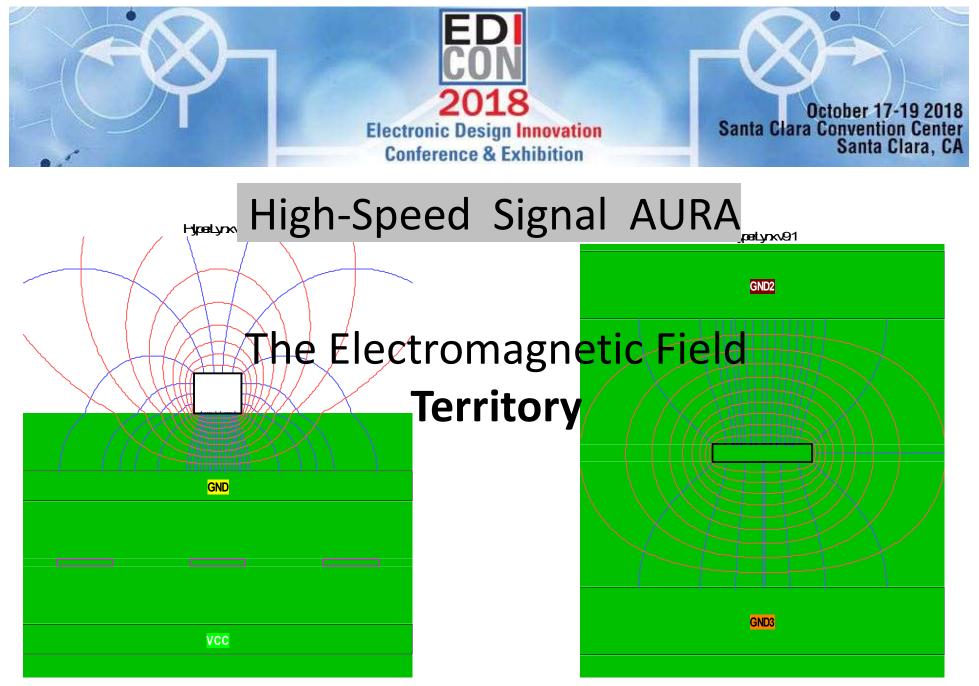

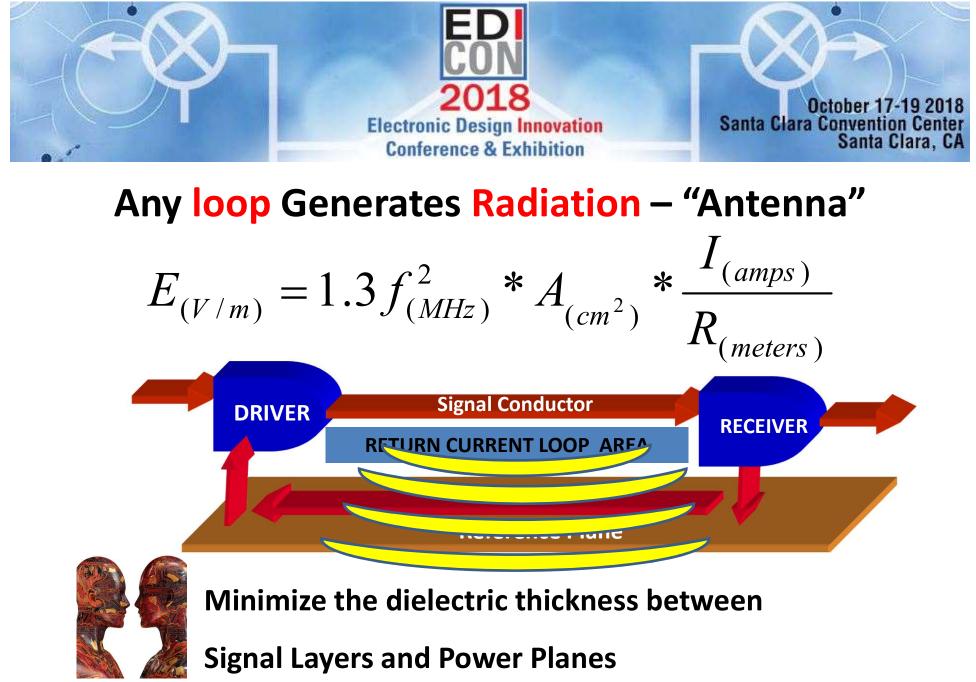

**Switching Signals radiates Electromagnetic Fields**

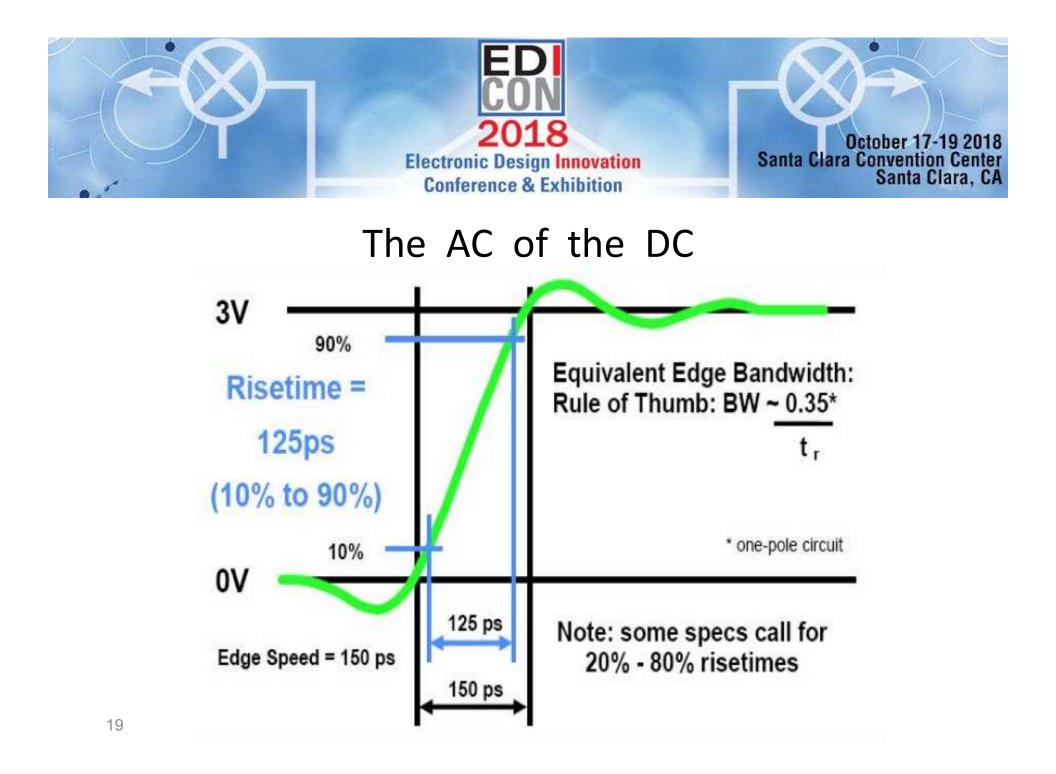

## The Switching Time

## During Switching time [tR, tF]

dV/dt Causes Electric Field Capacitance dI/dt Causes Magnetic Field Inductance

#### The Signal has the potential to be an Electromagnetic Field propagating between the Conductor and the Reference Planes

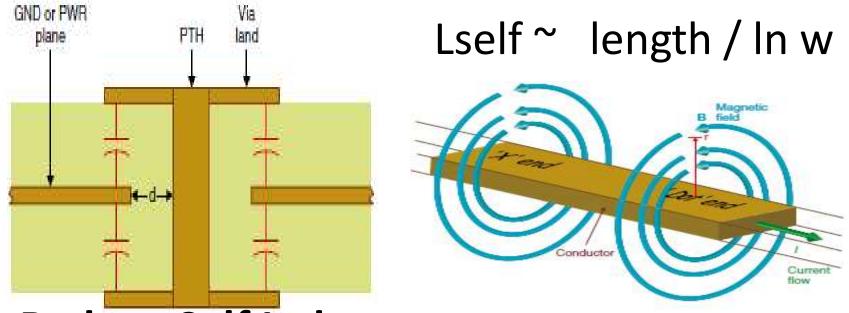

## Electric Fields and Self Inductance during Switching Time [Rise Time or Fall Time]

Reduce Self Inductance of Conductors by

<sup>21</sup> minimizing length and/or by maximizing width

Shalom-Shlomi-Zigdon@iTech-iCollege.com

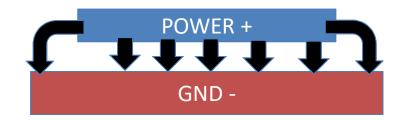

GND PLANE

**Hi-Speed Return Current**

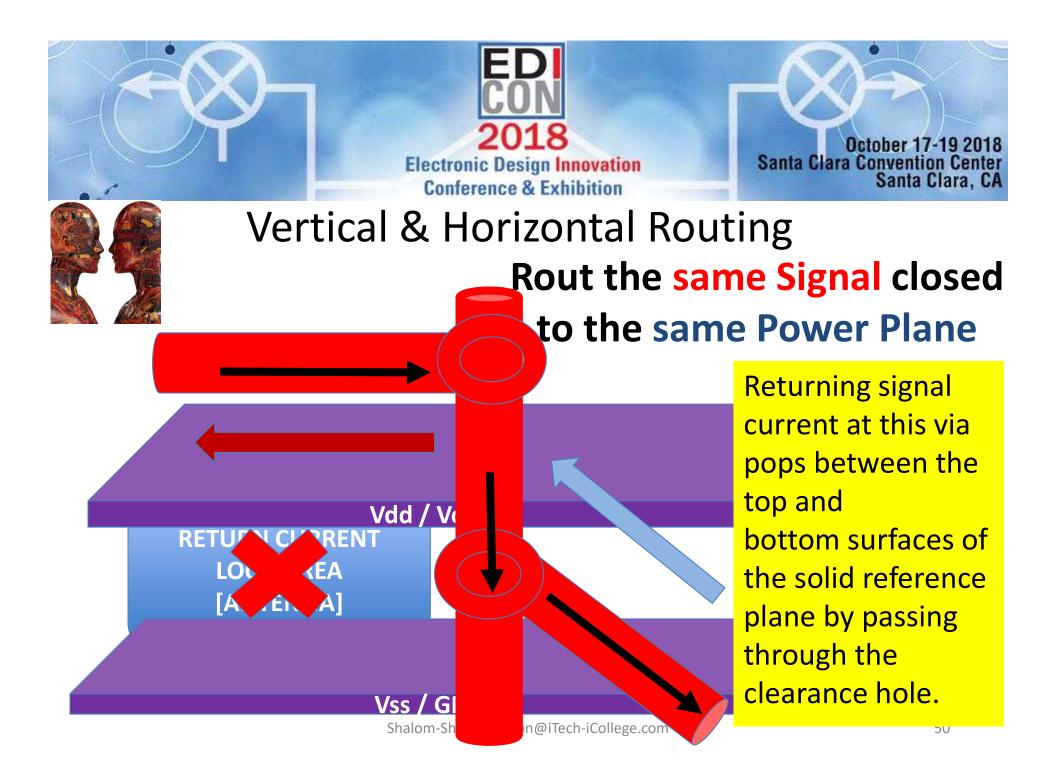

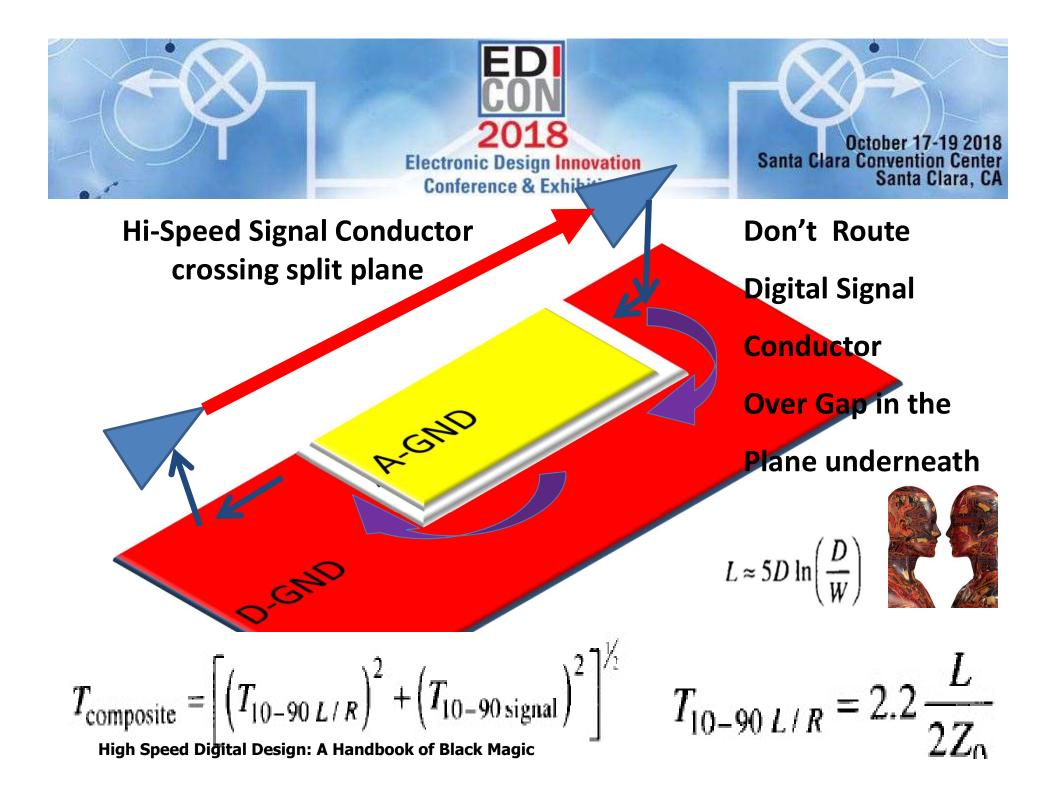

For F>100 KHz, the Signal Returns through lowest Inductance (Loop Area) and highest Capacitance The PCB layout sets the Return Current Path

## **Return current path** =Shortest possible connection

AC

DC

Less Resistance

Less Impedance

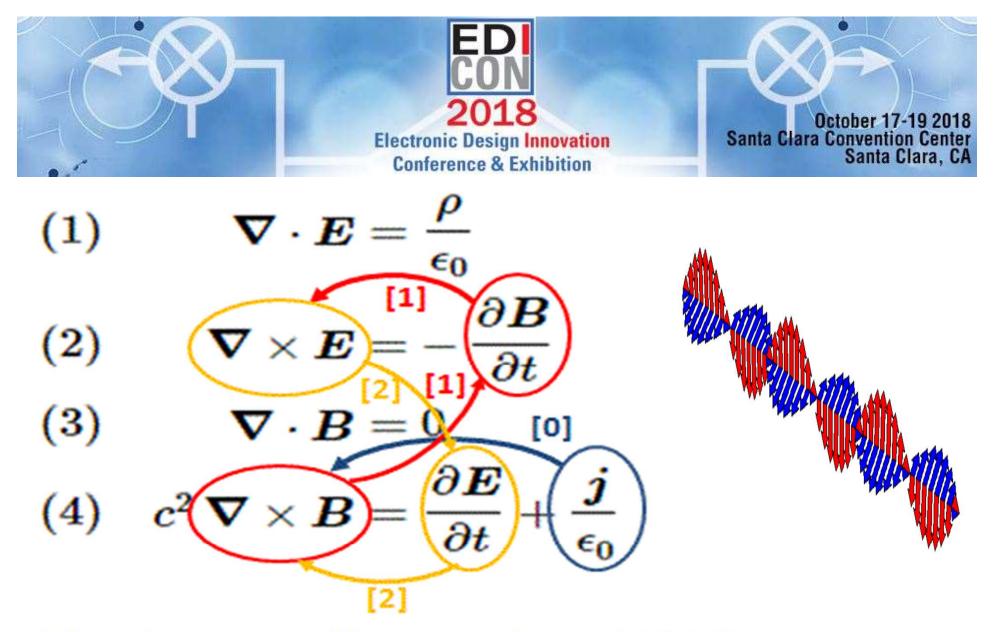

## James Clerk Maxwell

#### Maxwell's Equations

- 1. Guass's Law The greater the charge, the greater the electric field

- 2. Guass's Law for magnetism -Magnetic flux is zero through a closed surface

- 3. Faraday's Law An electric field is produced by a changing magnetic field

- 4. Ampere-Maxwell Law A magnetic field is produced by a changing electric field (moving charge)

[0] An electric current (*j*) causes circulation of B ( $\nabla \times B$ ) [1] A changing magnetic field ( $\partial B/\partial t$ ) causes circulation of E ( $\nabla \times E$ ) [2]<sup>2</sup>A changing electric field ( $\partial E/\partial t$ ) causes circulation of B ( $\nabla \times B$ )

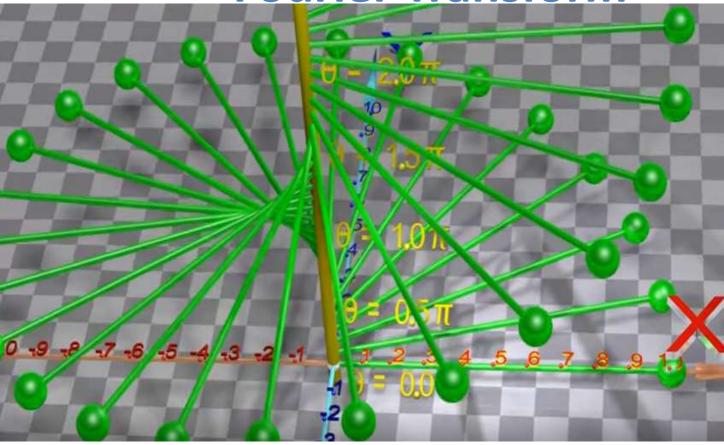

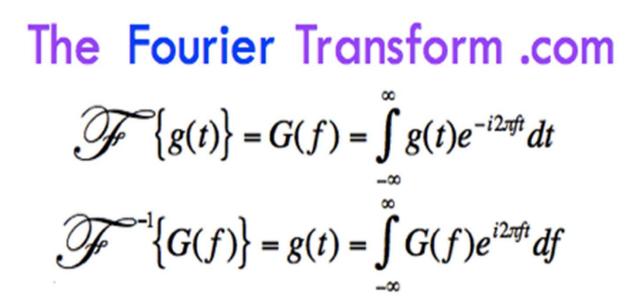

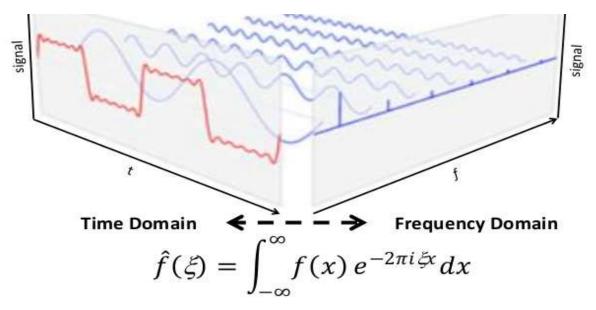

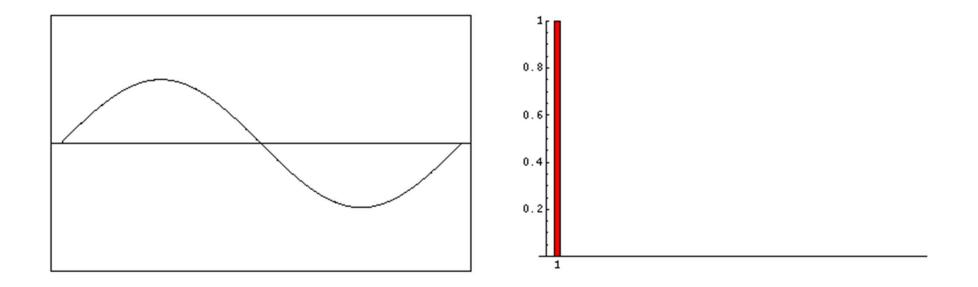

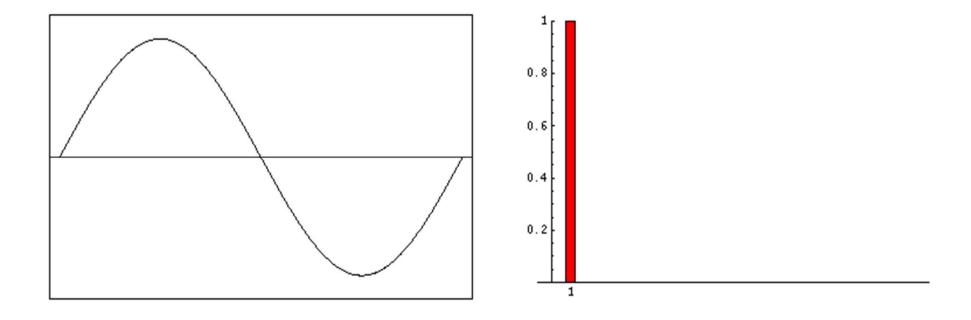

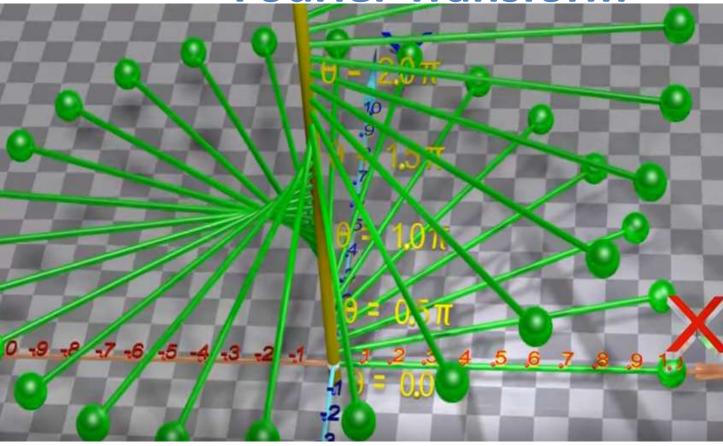

# **The Fourier Transform**

Shalom-Shlomi-Zigdon@iTech-iCollege.com

## Signal on Time Domain is a sum of infinite Analog Waves on Frequency Domain

Shalom-Shlomi-Zigdon@iTech-iCollege.com

**Fourier composition of a square wave**

29

Shalom-Shlomi-Zigdon@iTech-iCollege.com www.Board-Design-Academy

## Fourier Transform

(c) Each section is represented by an equivalent circuit

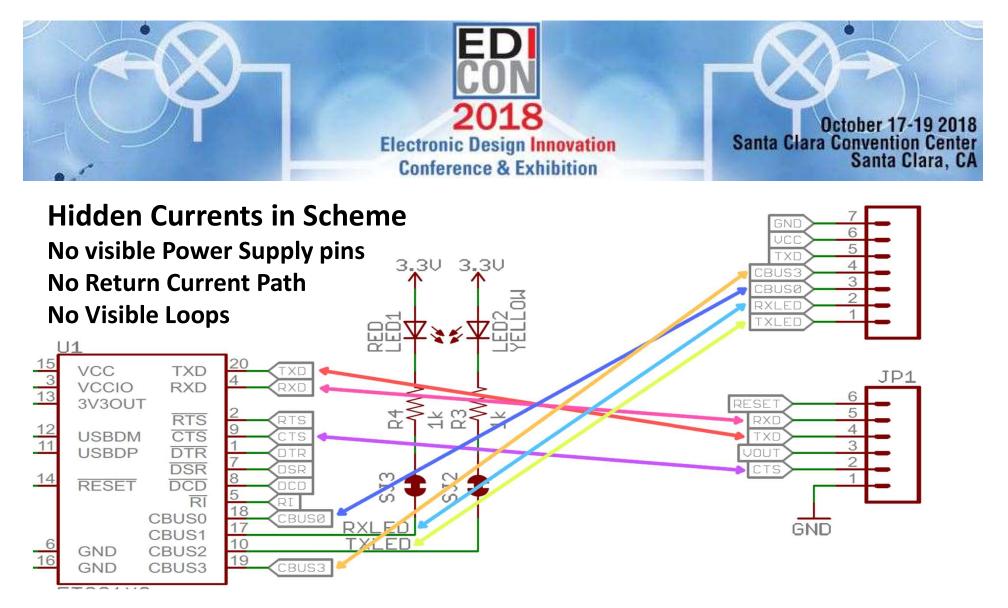

# As a result, the R&D Engineer, fails to communicate essential information to the PCB Designer

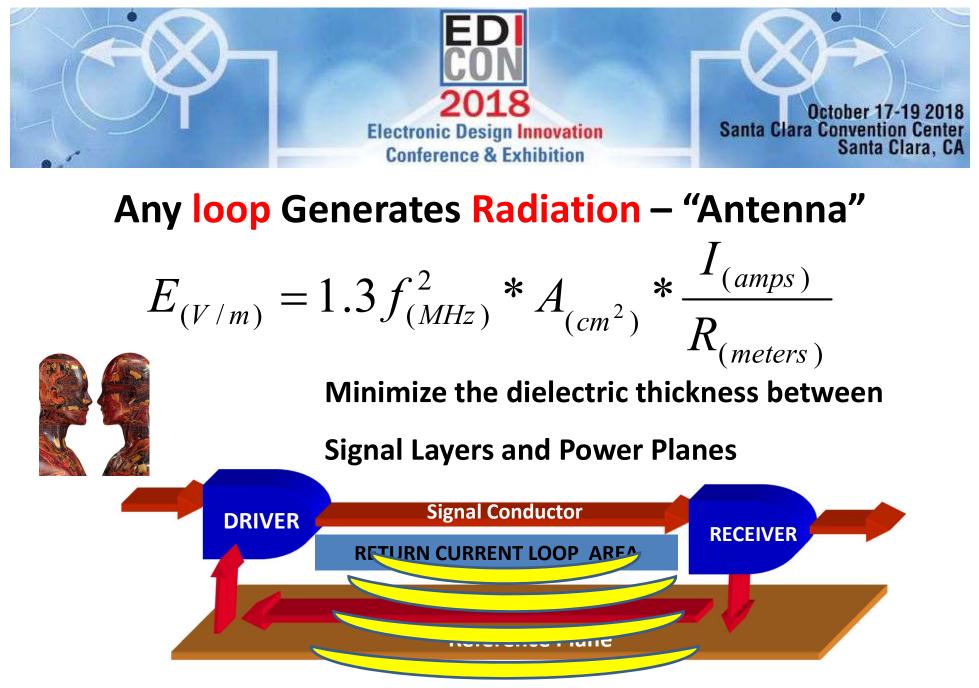

Today, in Digital Design, any "Line" in Schema is actually a Loop in the PCB/System behaving as an "Unwanted Antenna"

Shalom-Shlomi-Zigdon@iTech-iCollege.com

from Ohm/Kirchhoff to Maxwell ?

When Conductor Length is greater than

# T.E.L/10

### [not TEL/2, not TEL/4, not TEL/6]

- T.E.L = Transmission Electrical Length

- = the Distance a Signal E.M. Field [not the Current] propagates during its Switching Time

- FR4 D.K=4 6" in 1 nSecond

- So, for Tr= 1 nS

keep your Conductors 0.6" w/o Termination

### **Estimate the "Hidden Current" of the Hi-Speed Signals**

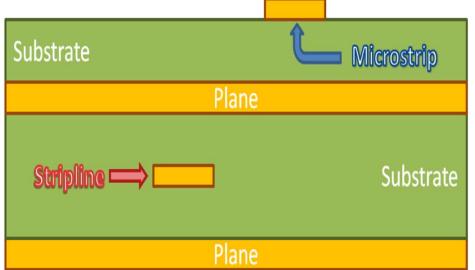

### The Six options:

Microstripe closed to GND Plane Low-to-High Transition, High -to- Low Transition Microstripe closed to VCC Plane Low-to-High Transition, High -to- Low Transition Stripline between Power Planes Low-to-High Transition, High -to- Low Transition

### The hidden parts of the Signal Path

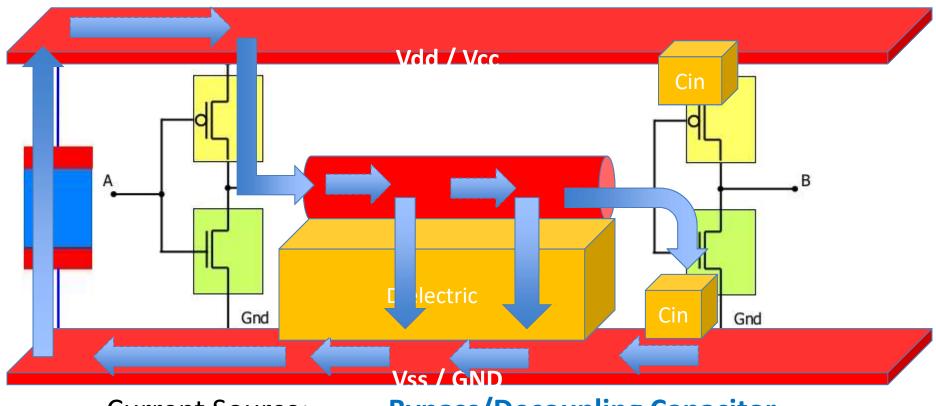

### Trace Adjacent to a Ground Plane (Microstrip) - Low-to-High Transition

Current Source:Bypass/Decoupling CapacitorReturn Current Path: Sh GND Vss CoPlane

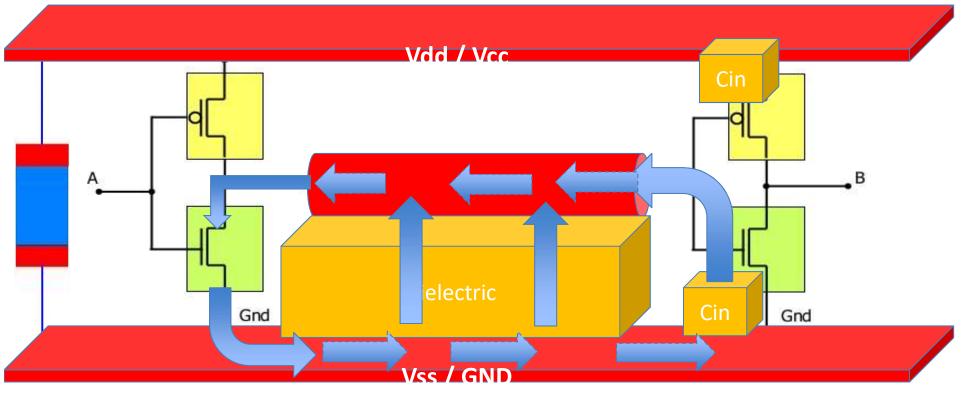

### Trace Adjacent to a Ground Plane (Microstrip) High -to- Low Transition

Current Source: Parasitic Capacitance Shalom-Shlomi-Zigdon@iTech-iCollege.com Return Current Path: GND / Vss Plane

### Trace Adjacent to a Power Plane (Microstrip) Low-to-High Transition

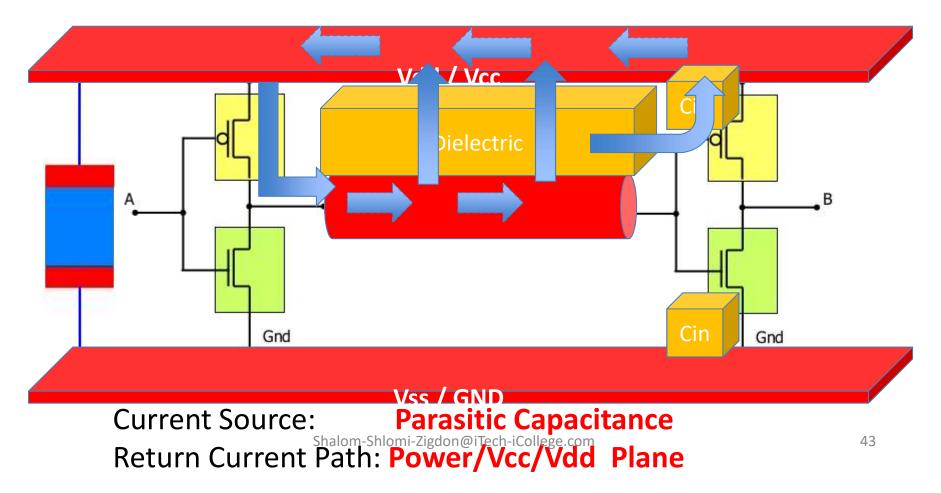

#### Trace Adjacent to a Power Plane (Microstrip) High -to- Low Transition

Return Current Patin: ShPower/Vcc/Vdd Plane

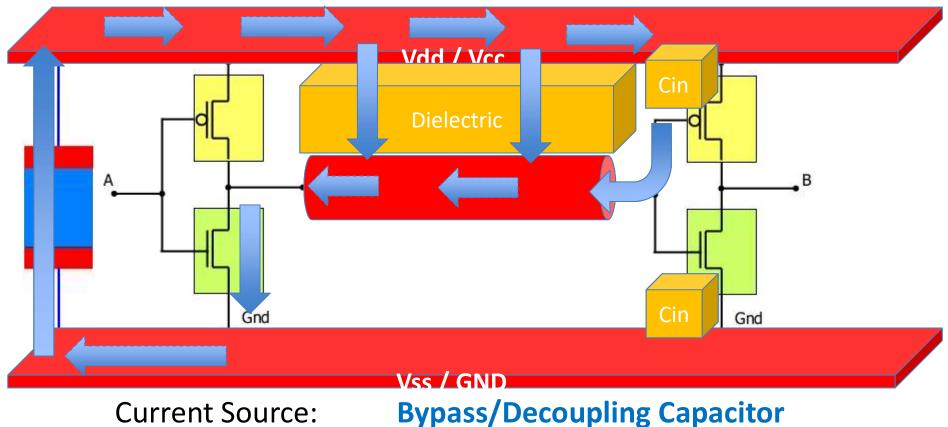

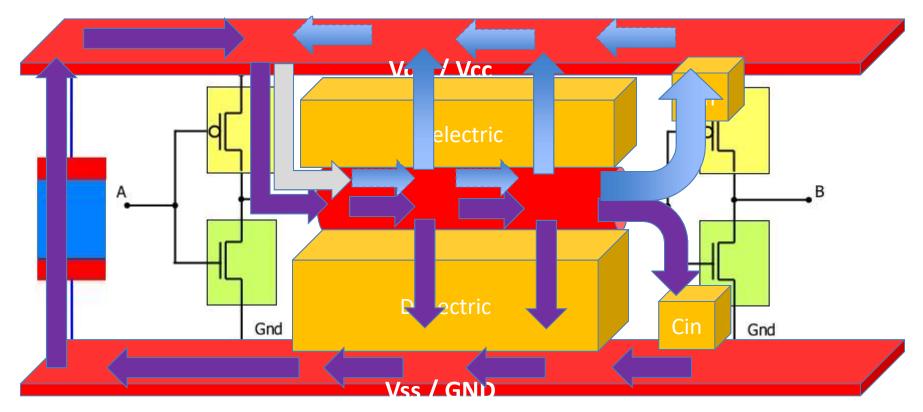

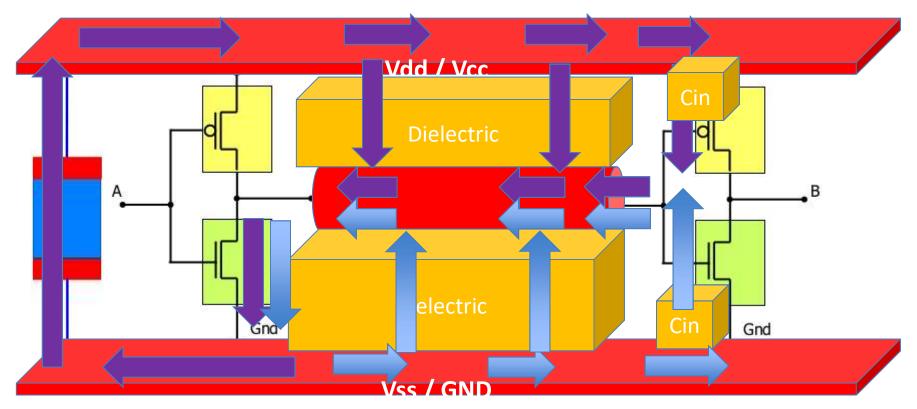

#### Trace Between a Power & Ground Planes (Stripline) Low-to-High Transition

Current Source: Bypass/Decoupling Capacitor & Parasitic Capacitance Shalom-Shlomi-Zigdon@iTech-iCollege.com Return Current Path: Power/Vcc/Vdd Plane & GND / Vss Plane

#### Trace Between a Power & Ground Planes (Stripline) High-to-Low Transition

Current Source: Bypass/Decoupling Capacitor & Parasitic Capacitance Shalom-Shlomi-Zigdon@iTech-iCollege.com Return Current Path: Power/Vcc/Vdd Plane & GND / Vss Plane

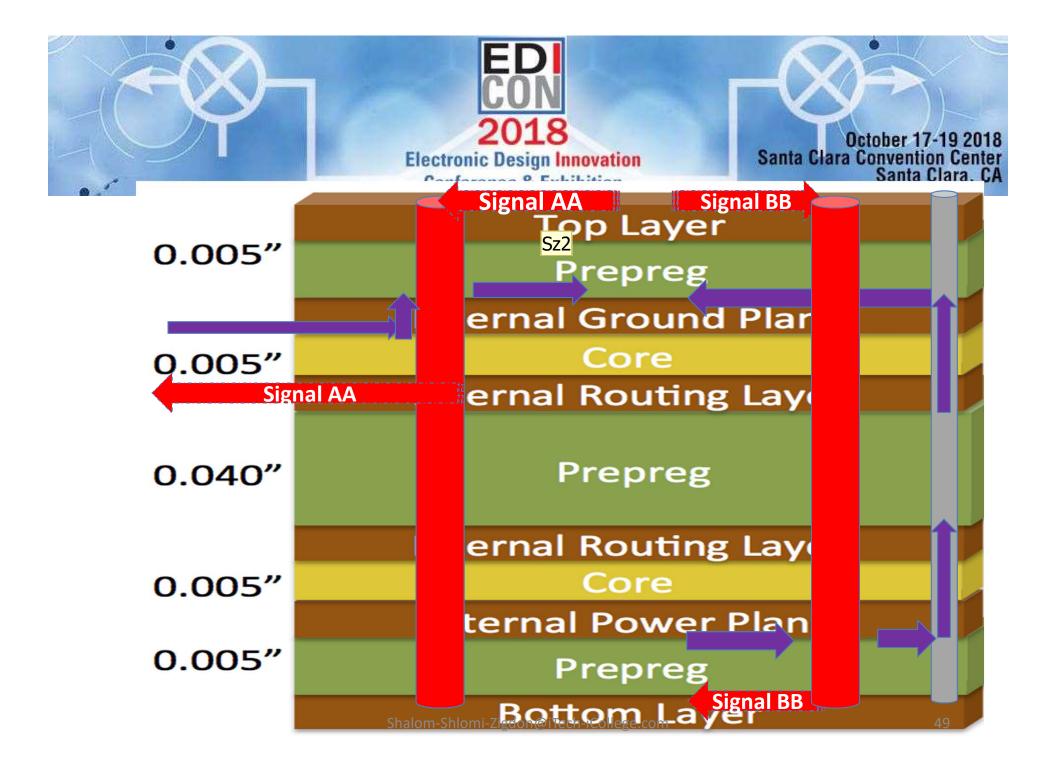

**Sz2** SHLOMI zigdon, 10/10/2018

### **Copper Balance**

### In case of non balance – fill the Signal Layers in GND Copper

### **Prevent Fringing Fields**

|  | 20 | Η | RU | LE |

|--|----|---|----|----|

|--|----|---|----|----|

### **Signal Groups Classes**

Sensitive

Noisy

### Natural

Lossy Lines [ needs low "loss-tangent/Dissipation Factor/ Tangent Delta"]

**High Speed Signals**

### Clocks

Differential Signals – "SEDRDES"

Communication – USB2, USB3, PCIexpress Gen 1/2/3/4, HDMI Video/Audio

### **Power Groups Classes**

### External Power Supply [not Filtered]

### Internal Power Supply [Filtered]

**Different Voltages level**

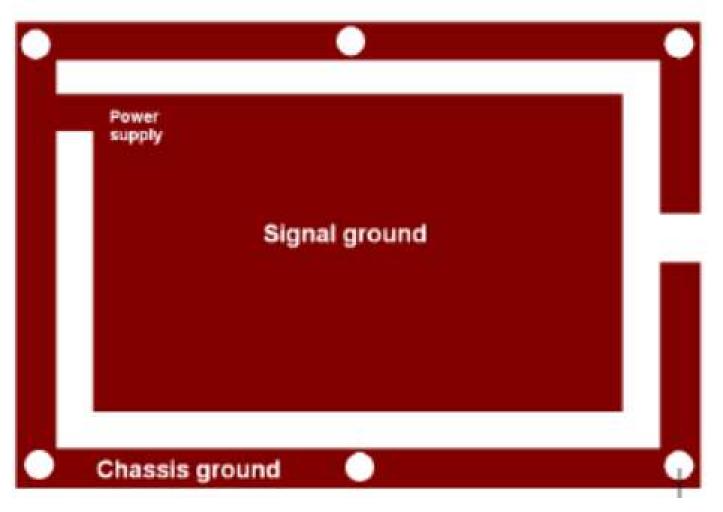

#### **Different Grounds on PCB**

Ground Tree, "Star-Point" placement [if Ground plane Splitted]

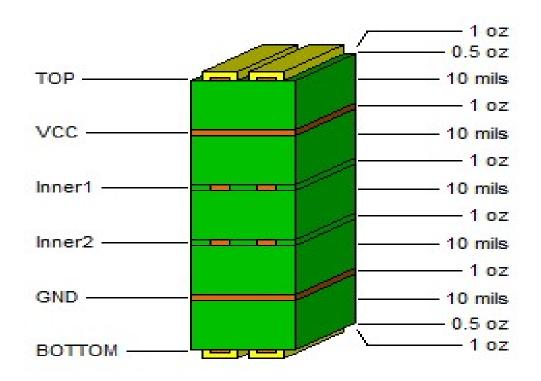

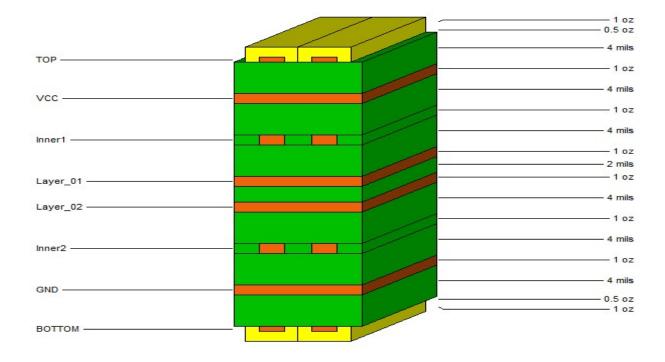

### internal Dual Stripline h=10

| Field Solver Stackup |        |        |         |                 |            |

|----------------------|--------|--------|---------|-----------------|------------|

| Туре                 | Thickr | ness l | Dielect | ric             | Layer      |

| Signal               | 2.0    | 2      | 1.00    |                 | TOP        |

| Die                  | el 1   | LO.00  | 4.      | <mark>30</mark> |            |

| Plane                | 1.3    | 5      | 4.30    | ١               | VCC        |

| Die                  | el 1   | LO.00  | 4.      | <mark>30</mark> |            |

| Signal               | 1.3    | 5      | 4.30    | Ir              | nner1      |

| Die                  | el 1   | LO.00  | 4.      | <mark>30</mark> |            |

| Signal               | 1.3    | 5      | 4.30    | Ir              | nner2      |

| Die                  | el 1   | LO.00  | 4.      | <mark>30</mark> |            |

| Plane                | 1.3    | 5      | 4.30    | Ģ               | <b>SND</b> |

| Die                  | el 1   | LO.00  | 4.      | <mark>30</mark> |            |

| Signal               | 2.0    | 2      | 1.00    | BC              | DTTOM      |

|                      |        |        |         |                 |            |

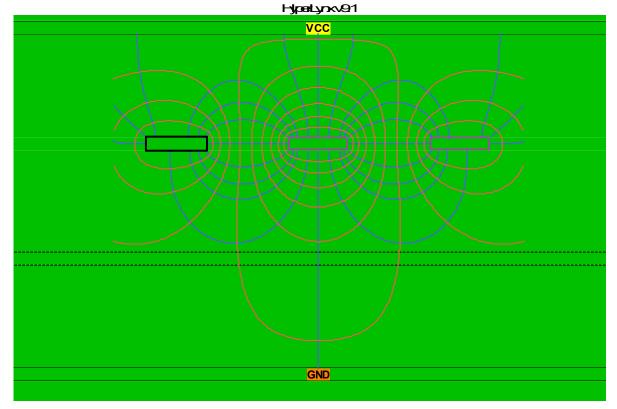

Layer Stackup. Design: xt\_trace\_separation.ffs. HyperLynx LineSim v9.1

Shalom-Shlomi-Zigdon@iTech-iCollege.com

Total thickness = 59.45 mils

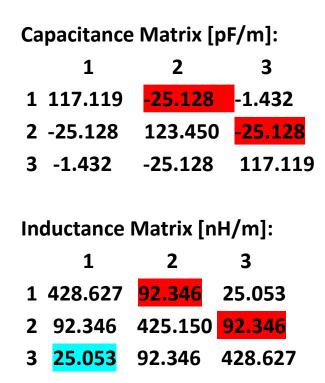

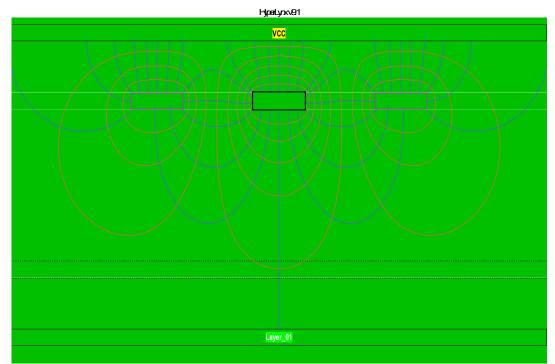

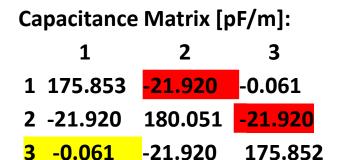

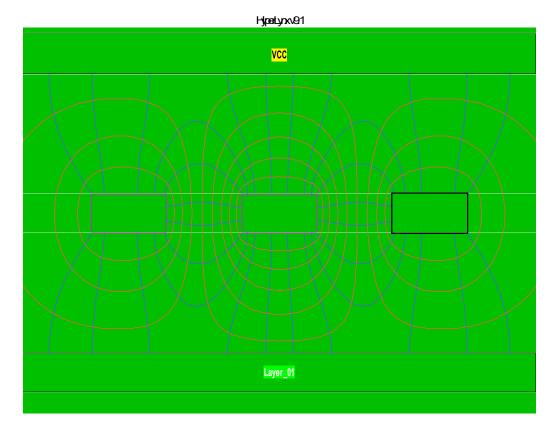

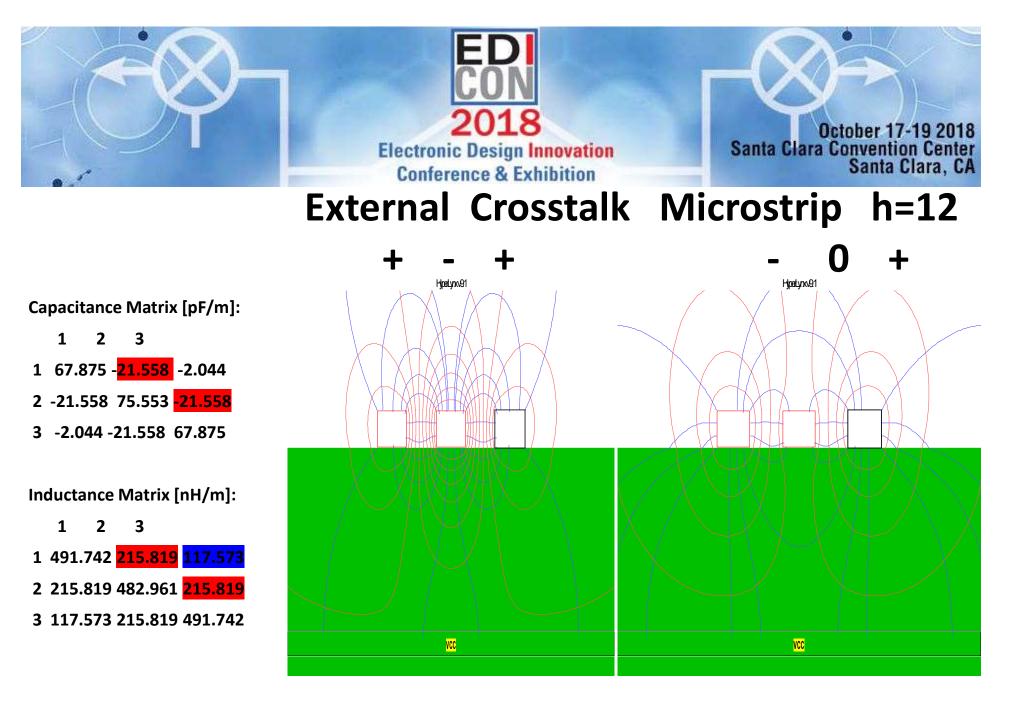

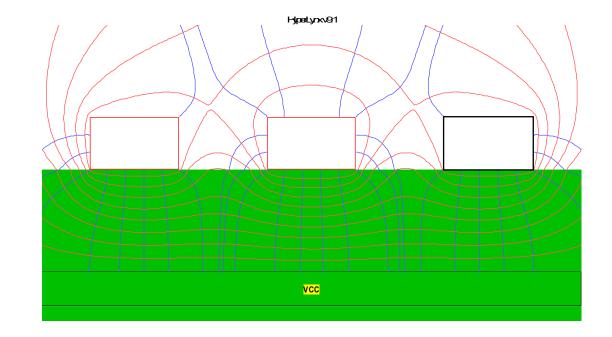

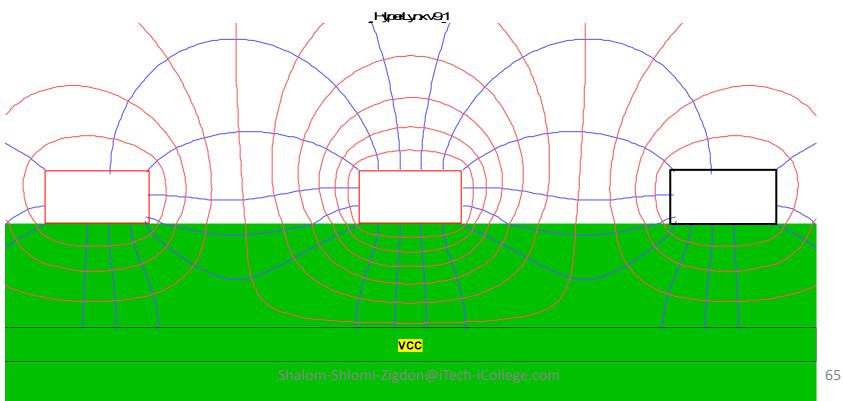

### Crosstalk internal Dual-Stripline 6/8/6/8/6 h=12 + - +

### Crosstalk internal Dual-Stripline 6/8/6/8/6 h=4 + - +

Capacitance Matrix [pF/m]:

|   | 1       | 2              | 3       |

|---|---------|----------------|---------|

| 1 | 165.191 | <b>-14.786</b> | -0.510  |

| 2 | -14.786 | 167.044        | -14.786 |

| 3 | -0.510  | -14.786 1      | 65.191  |

|   | 1       | 2                   | 3                   |

|---|---------|---------------------|---------------------|

| 1 | 291.977 | <mark>26.132</mark> | 3.240               |

| 2 | 26.132  | 291.042             | <mark>26.132</mark> |

| 3 | 3.240   | 26.132              | 291.977             |

# Crosstalk internal Balanced Stripline h=4

Shalom-Shlomi-Zigdon@iTech-iCollege.com

Total thickness = 38.15 mils

#### Inductance Matrix [nH/m]:

|   | 1       | 2                   | 3       |

|---|---------|---------------------|---------|

| 1 | 276.330 | <mark>34.172</mark> | 4.356   |

| 2 | 34.172  | 274.045             | 34.172  |

| 3 | 4.356   | 34.172              | 276.330 |

Crosstalk internal Balanced Stripline 4/4/4/4 h=12 + - +

### External Crosstalk h=4 Microstrip + + +

Capacitance Matrix [pF/m]:

|   | 1      | 2                   | 3                   |

|---|--------|---------------------|---------------------|

| 1 | 89.707 | <mark>-5.104</mark> | -0.611              |

| 2 | -5.104 | 90.167              | <mark>-5.104</mark> |

| 3 | -0.611 | -5.104              | 89.707              |

Inductance Matrix [nH/m]:

|   | 1       | 2                   | 3        |

|---|---------|---------------------|----------|

| 1 | 346.080 | <mark>51.467</mark> | 15.526   |

| 2 | 51.467  | 344.43              | 6 51.467 |

| 3 | 15.526  | 51.467              | 346.080  |

### Microstrip - External Layers EMI Radiation and External Crosstalk preferred h=< 4 mill

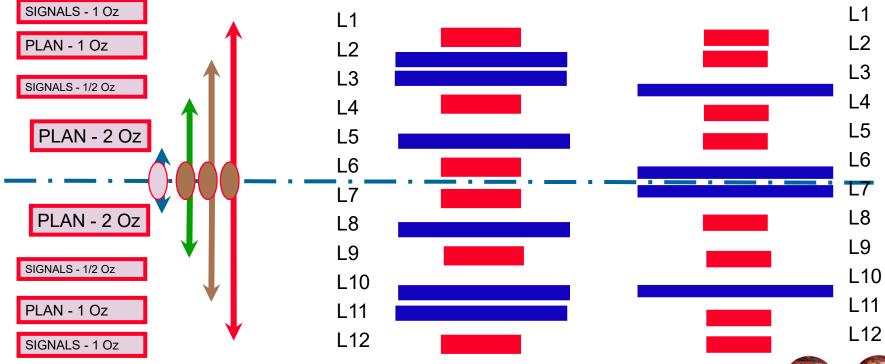

### More Power Layers – Better Pl

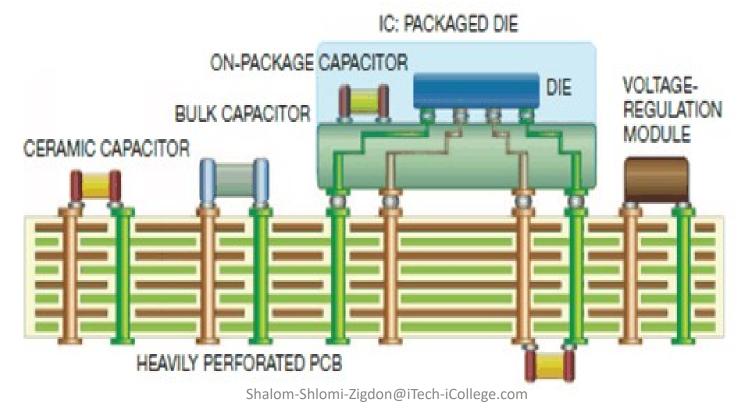

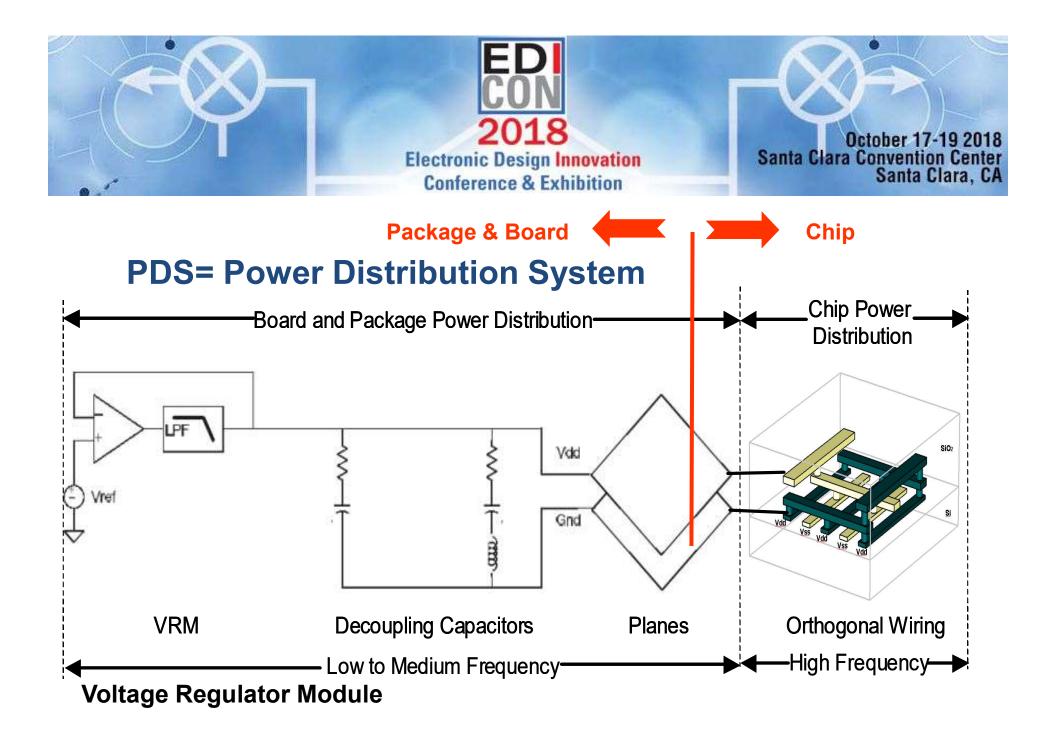

### **PDN World controlled by Capacitors and Capacitance**

# **Power Conductors rules for EMC & SI**

**Worst** long & Thin Conductor Higher Self-Inductance >> EMI

**Better** Short & Wide Conductor Minimize Self-Inductance

**Preferred** 3 Vias act as 3 Inductors in Parallel result as 1/3 Self Induction

# Bypass/Decoupling Capacitors

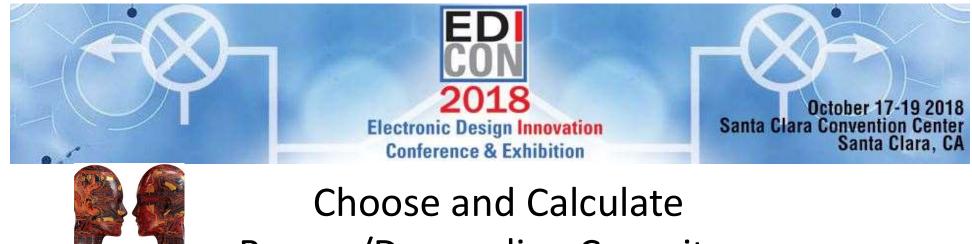

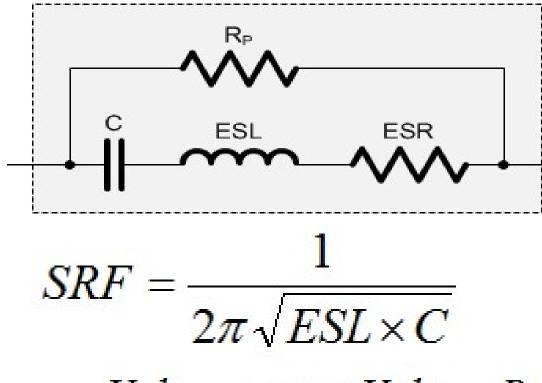

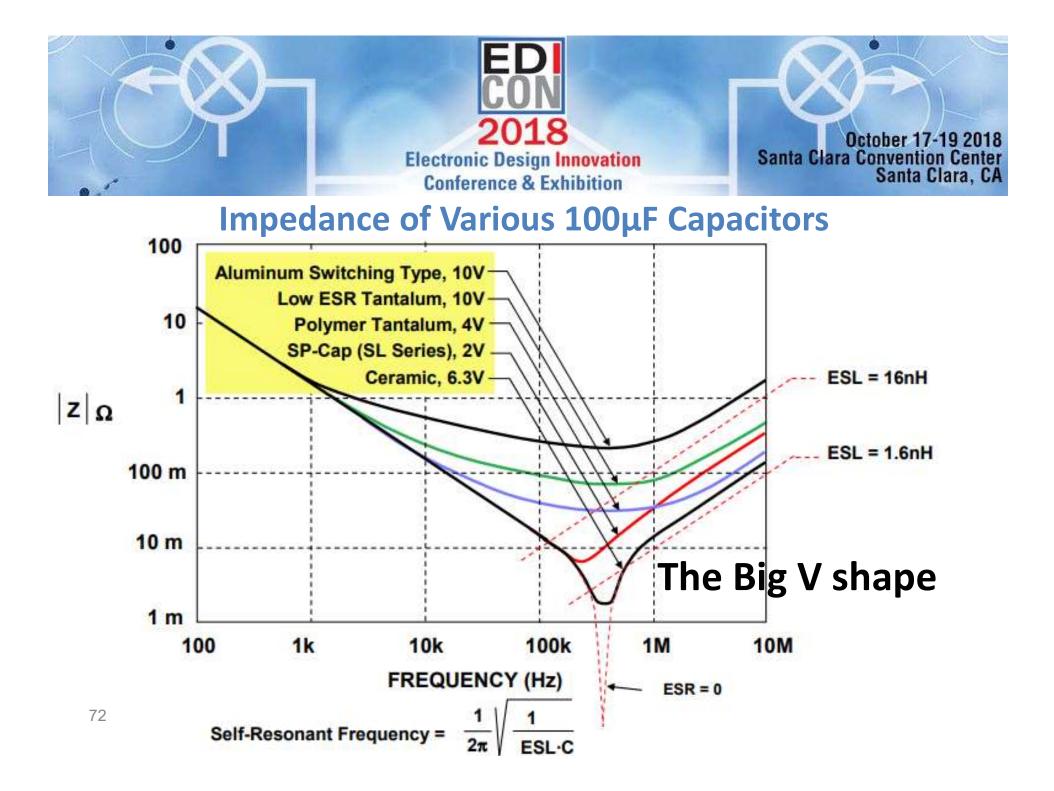

All capacitors shares a common electrical module with 4 main components

- 1. Capacitance

- 2. Spark gap [DC Working Volatge much larger than nominal voltage]

- 3. ESR Equivalent Serious Resistance [contacts, leads, charging and discharging causes heat]

- 4. ESL Equivalent Serial Inductance [due to self inductance of leads, current loops inside the package]

High Frequency noise – ESL most important

$$z_c = x_L + x_c + R = J2\pi FL + 1/j2\pi FC + R$$

# **The Real Capacitor**

The decoupling capacitor is an obstacle for the highfrequency components of the return current because the associated inductance makes the equivalent impedance of the capacitor too high

= Voltage × max VoltageRipple TransientCurrent 7 =

### $z_c = x_L + x_c + R = J2\pi FL + 1/j2\pi FC + R$

### requency

Low Self-Resonance High

### *impedance* Capacitive Resistive Inductive

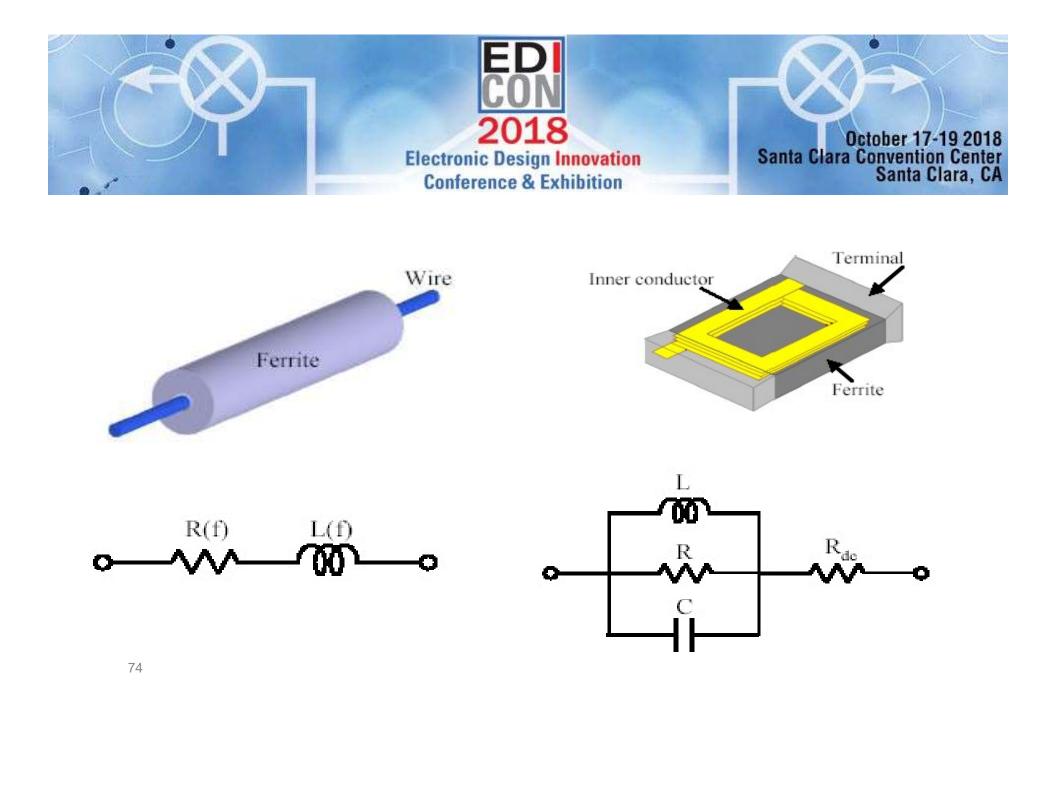

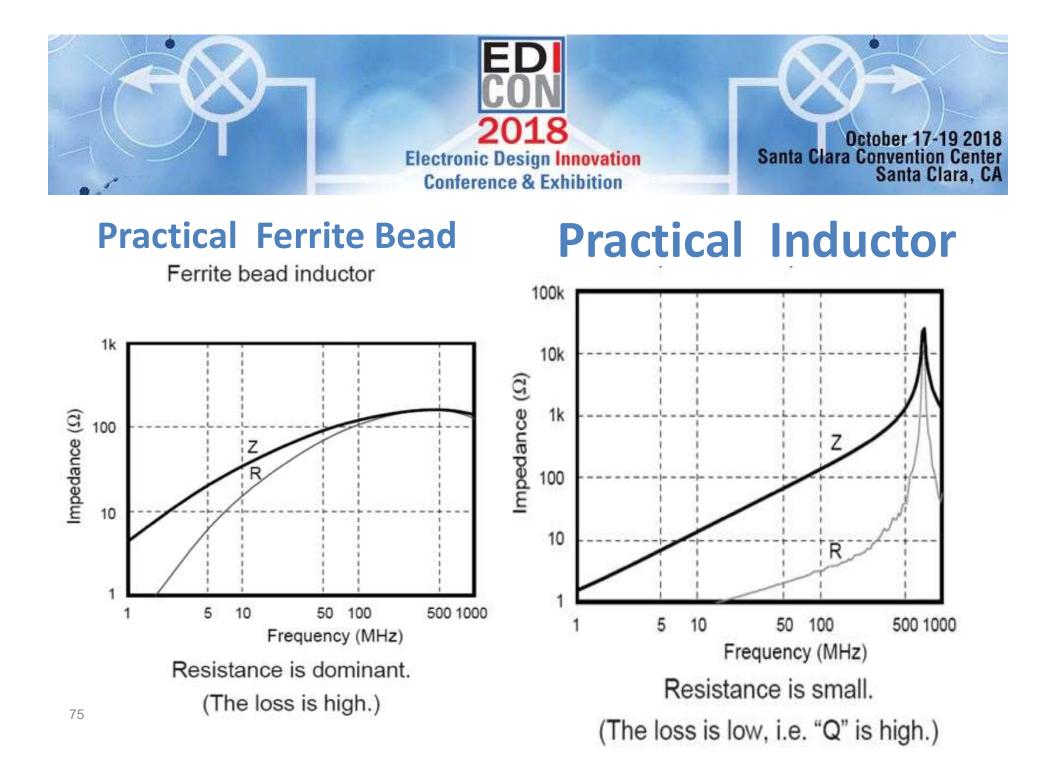

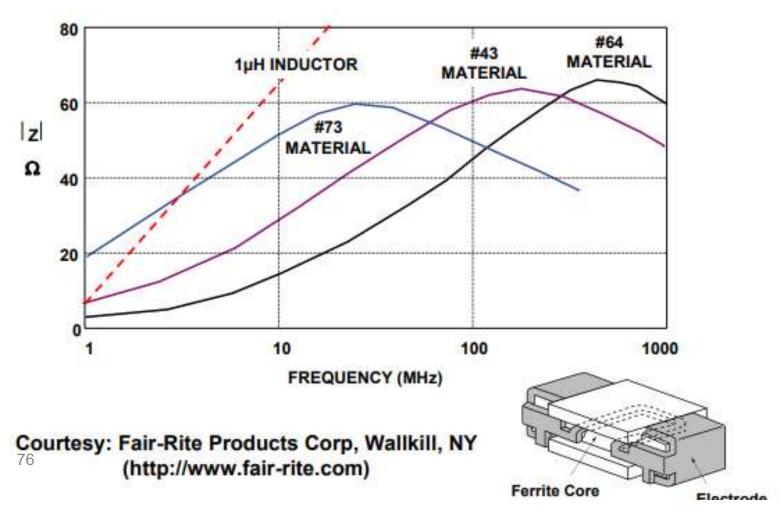

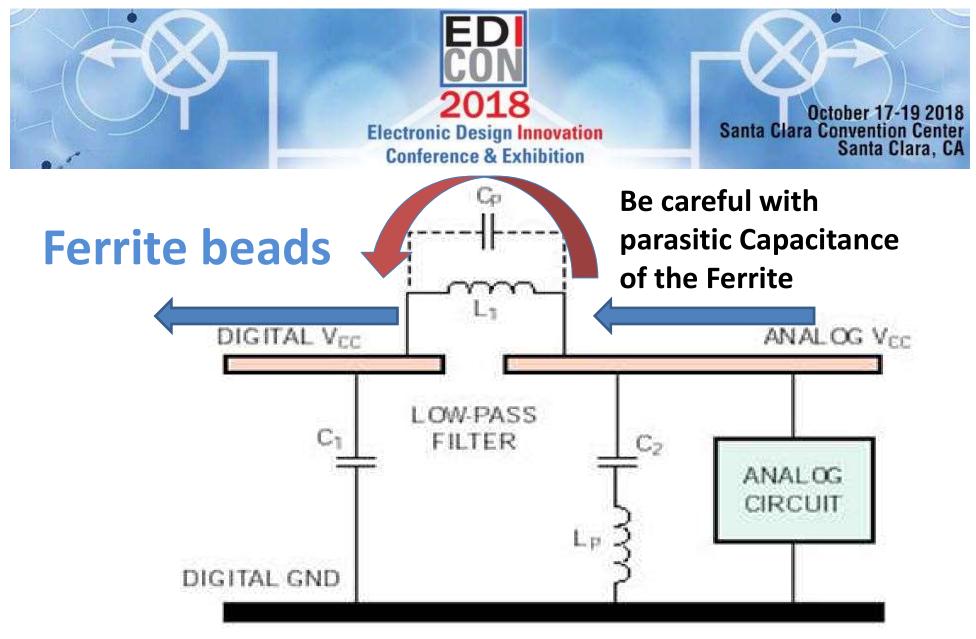

#### Ferrite Bead Impedance Compared to a 1µH Inductor

Drawing: courtesy EDN Magazine

+ Engineering/PCB/Technologist Better be a part of a Team Than a group of people doing Team Work

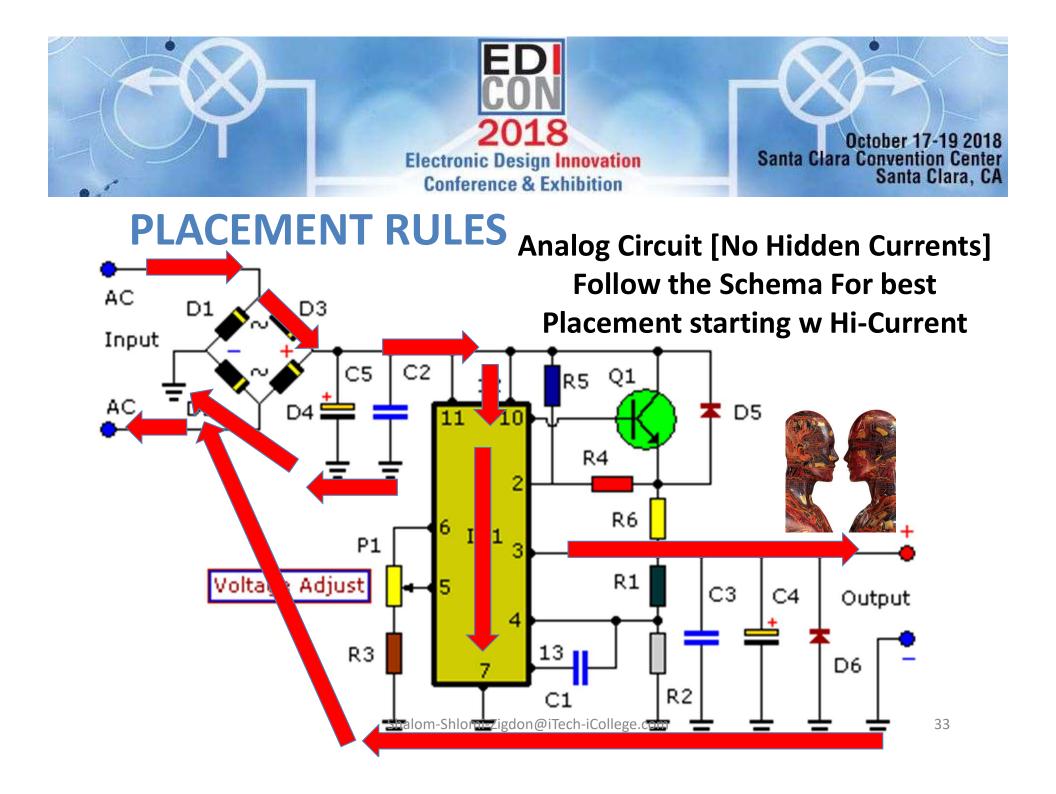

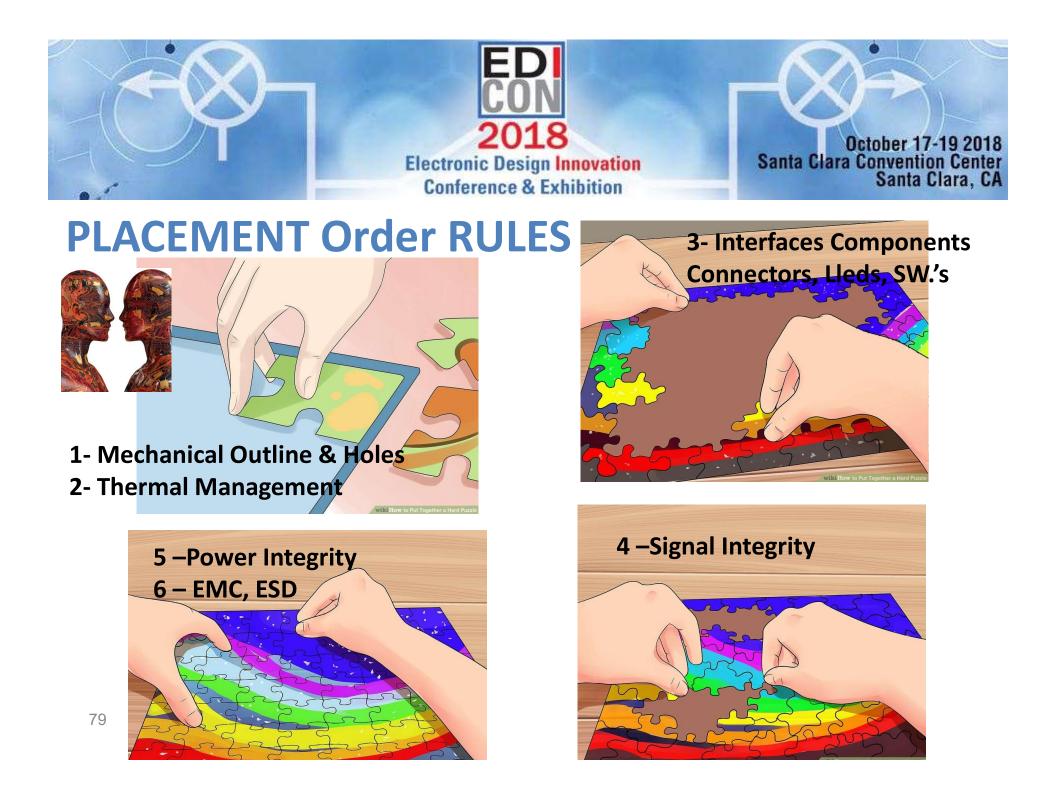

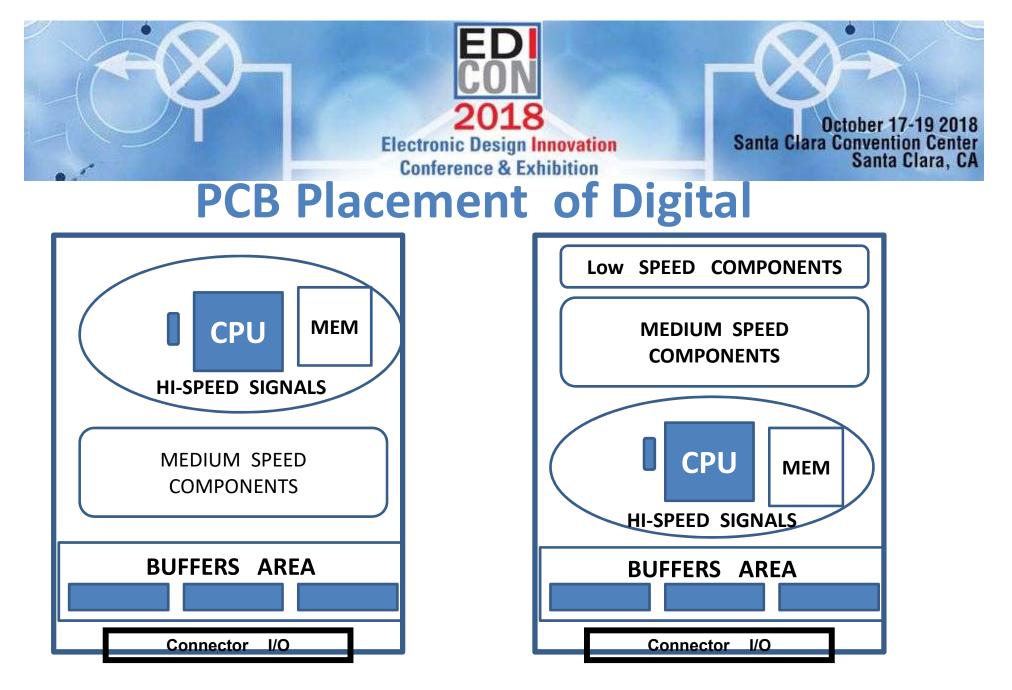

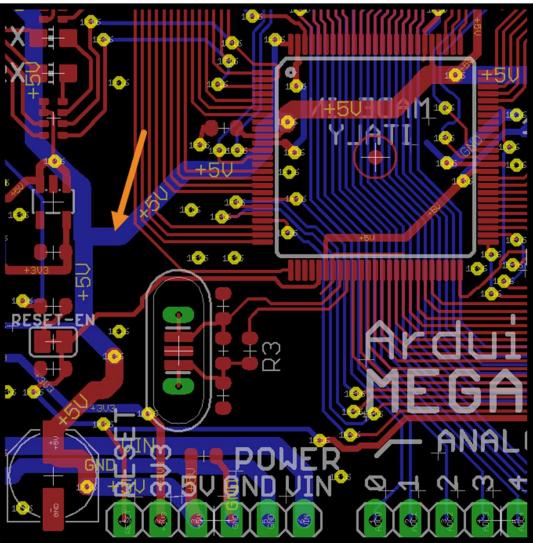

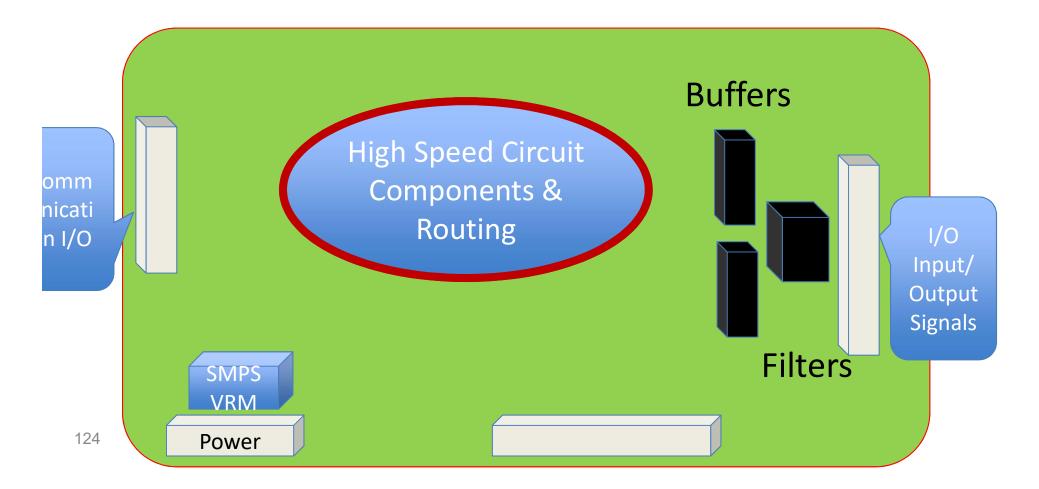

# **PLACEMENT RULES**

High-Speed Board Start with microP/microC in the middle, far away from the I/O Connectors

# **PLACEMENT RULES**

No microP/microC?

Place outside the PCB Outline each Group according the Schema pages

# Design Your Power and Ground Traces Wider

## **Traces Matching for DATA/Add**

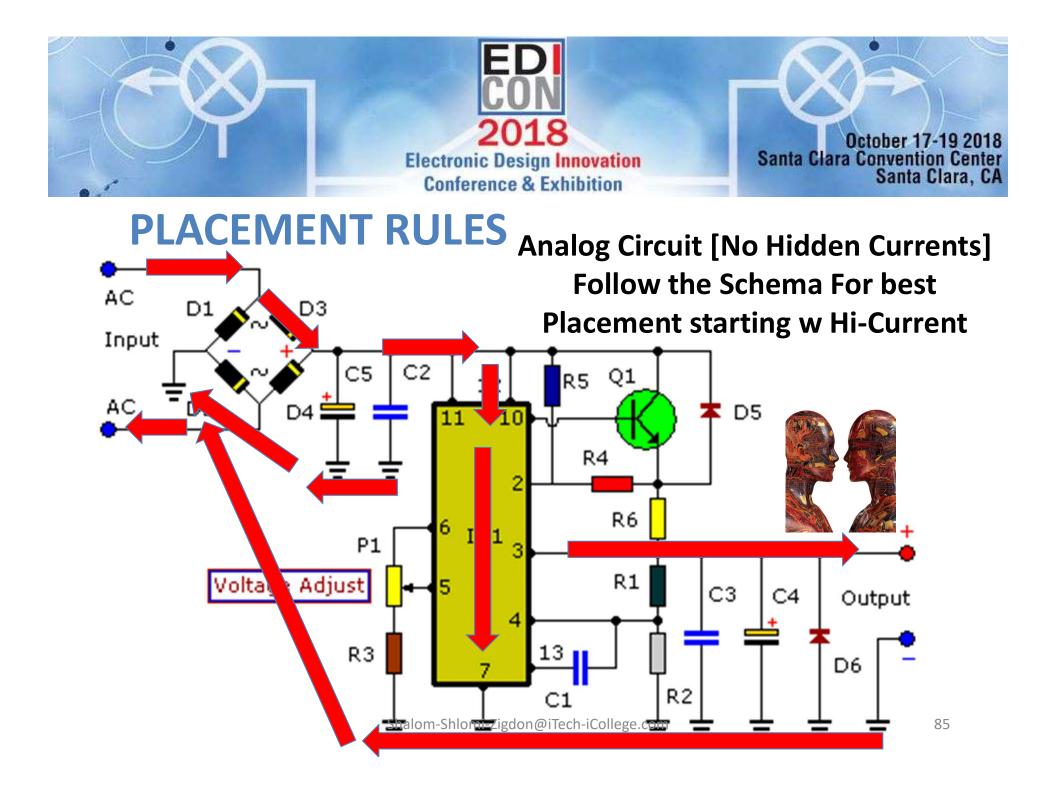

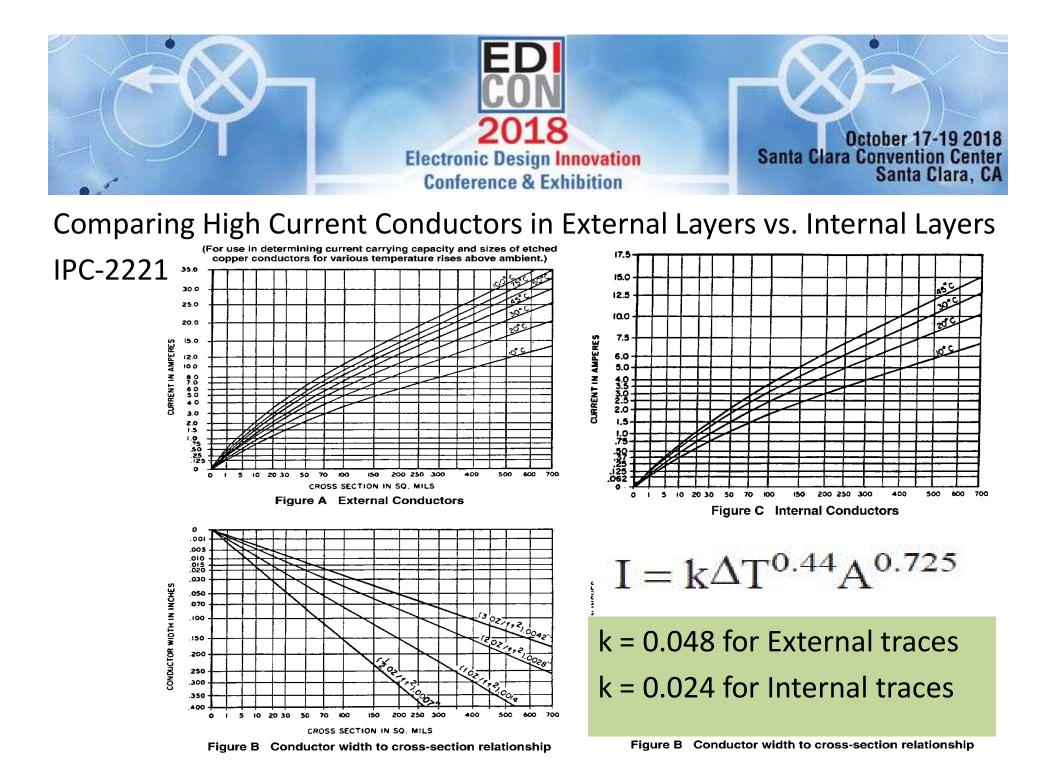

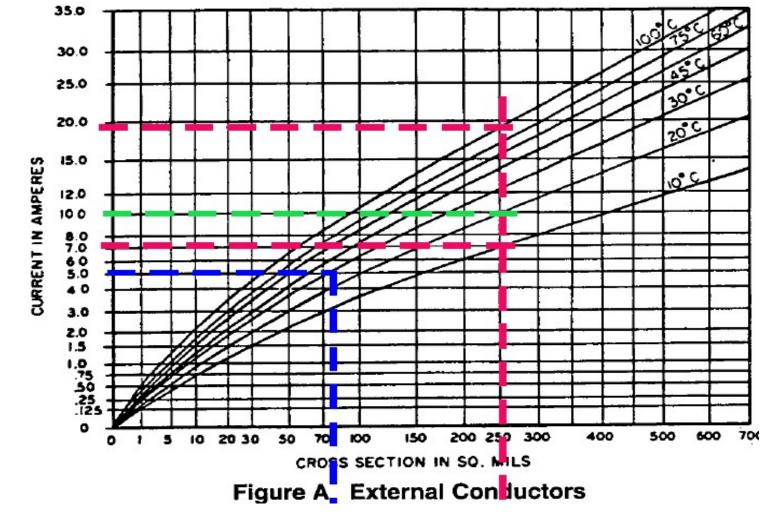

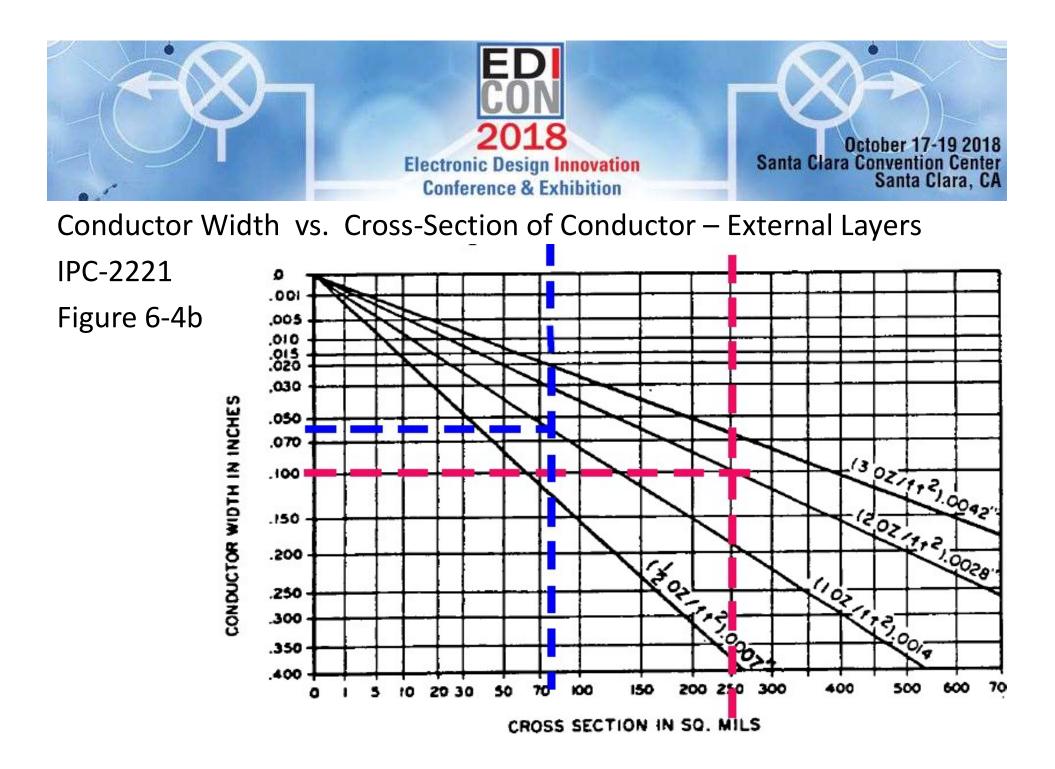

### **PLACEMENT RULES – Analog Circuit**

- 1. Identufy the Critical Path

- 2. Start with the High-Current Conductors, During Placement

- 3. Calculate width according to Current and added Temperature allowed as short as possible

- 4. Rout from pin to pin **WITHIN** the group on **External layers**

- 5. Rout **BETWEEN groups** will be done on **INNER layers**

- 6. Order of placement depends on number of Component pins on <sup>86</sup>the Critical Path

Current vs. Cross-Section of Conductor – External Layers

IPC-2221 Figure 6-4a

|                | <b>Ø</b> -           |             | Electronic Design Innovation<br>Conference & Exhibition | s              | anta Clara          | ctober 17-19 2<br>Convention Cer<br>Santa Clara, |

|----------------|----------------------|-------------|---------------------------------------------------------|----------------|---------------------|--------------------------------------------------|

|                |                      | er Proce    | <u></u>                                                 |                |                     | l Thickne                                        |

| Inte           | rnal La              | yer Foil    | <b>IPC-2151</b>                                         | After Plating  |                     |                                                  |

| Copper<br>Foil | м                    | inimum      | PCB Cross Section<br>Before Etch                        | Copper<br>Foil | Mini                | imum                                             |

| 1/8 oz         | <b>3.5 μm</b>        | 0.000138 in | Resist Resist                                           | 1/8 oz         | 20 µm               | 0.000787                                         |

| 1⁄4 oz         | <mark>6.</mark> 0 μm | 0.000236 in | Copper                                                  | 1⁄4 oz         | 20 µm               | 0.000787                                         |

| 3/8 oz         | <mark>8</mark> .0 μm | 0.000315 in | Laminate                                                | 3/8 oz         | 25 μm               | 0.000984                                         |

| ½ oz           | 12.0 µm              | 0.000472 in |                                                         | ½ oz           | <mark>33 μ</mark> m | 0.001299                                         |

| 1 oz           | 25.0 µm              | 0.000984 in |                                                         | 1 oz           | 46 µm               | 0.001811                                         |

| 2 oz           | <mark>56.0</mark> μm | 0.002205 in | After Etch<br>Resist Resist                             | 2 oz           | 76 μm               | 0.002992                                         |

| 3 oz           | <mark>91.0</mark> μm | 0.003583 in | Copper Copper                                           | 3 oz           | <b>107</b> μm       | 0.004213                                         |

|                | 28                   | 8           |                                                         | 4 oz           | <b>1</b> 37 μm      | 0.005394                                         |

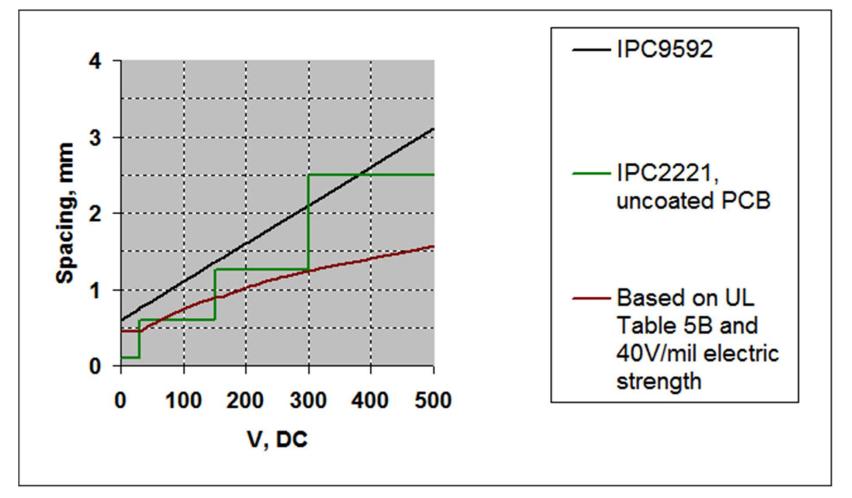

## **Conductors clearance vs voltage**

#### Table 6-1 Electrical Conductor Spacing

Voltage Between Conductors (DC or AC

Peaks)

0-15

16-30

31-50

51-100

101-150

151-170

171-250

251-300

301-500

> 500 See para. 6.3

for calc.

**B1**

0.05 mm

[0.00197 in]

0.05 mm [0.0197 in]

0.1 mm [0.0039 in]

0.1 mm [0.0039 in]

0.2 mm [0.0079 in]

0.2 mm [0.0079 in]

0.2 mm [0.0079 in]

0.2 mm

[0.0079 in]

0.25 mm

[0.00984 in]

0.0025 mm

/volt

2.5 mm

[0.0984 in]

0.005 mm

/volt

12.5 mm

[0.4921 in]

0.025 mm

/volt

| Minimum Spacing |             |             |              |                      |                            |              |  |

|-----------------|-------------|-------------|--------------|----------------------|----------------------------|--------------|--|

|                 | Bare        | Board       |              | Assembly             |                            |              |  |

|                 | B2 B3       |             | B4           | A5                   | A6                         | A7           |  |

| ]               | 0.1 mm      | 0.1 mm      | 0.05 mm      | 0.13 mm              | 0.13 mm                    | 0.13 mm      |  |

|                 | [0.0039 in] | [0.0039 in] | [0.0197 in]  | [0.00512 in]         | [0.0051 <mark>2 in]</mark> | [0.00512 in] |  |

| 0               | 0.1 mm      | 0.1 mm      | 0.05 mm      | 0.13 mm              | 0.25 mm                    | 0.13 mm      |  |

|                 | [0.0039 in] | [0.0039 in] | [0.0197 in]  | [0.00512 in]         | [0.00984 in]               | [0.00512 in] |  |

|                 | 0.6 mm      | 0.6 mm      | 0.13 mm      | 0.13 mm              | 0.4 mm                     | 0.13 mm      |  |

|                 | [0.024 in]  | [0.024 in]  | [0.00512 in] | [0.00512 in]         | [0.016 in]                 | [0.00512 in] |  |

| Ĭ.              | 0.6 mm      | 1.5 mm      | 0.13 mm      | 0.13 mm              | 0.5 mm                     | 0.13 mm      |  |

|                 | [0.024 in]  | [0.0591 in] | [0.00512 in] | [0.00512 in]         | [0.020 in]                 | [0.00512 in] |  |

| Children .      | 0.6 mm      | 3.2 mm      | 0.4 mm       | 0. <mark>4</mark> mm | 0.8 mm                     | 0.4 mm       |  |

|                 | [0.024 in]  | [0.126 in]  | [0.016 in]   | [0.016 in]           | [0.031 in]                 | [0.016 in]   |  |

| 0               | 1.25 mm     | 3.2 mm      | 0.4 mm       | 0.4 mm               | 0.8 mm                     | 0.4 mm       |  |

| 0               | [0.0492 in] | [0.126 in]  | [0.016 in]   | [0.016 in]           | [0.031 in]                 | [0.016 in]   |  |

|                 | 1.25 mm     | 6.4 mm      | 0.4 mm       | 0.4 mm               | 0.8 mm                     | 0.4 mm       |  |

|                 | [0.0492 in] | [0.252 in]  | [0.016 in]   | [0.016 in]           | [0.031 in]                 | [0.016 in]   |  |

|                 | 1.25 mm     | 12.5 mm     | 0.4 mm       | 0.4 mm               | 0.8 mm                     | 0.8 mm       |  |

|                 | [0.0492 in] | [0.4921 in] | [0.016 in]   | [0.016 in]           | [0.031 in]                 | [0.031 in]   |  |

0.8 mm

[0.031 in]

0.00305 mm

/volt

1.5 mm

[0.0591 in]

0.00305 mm

/volt

0.8 mm

[0.031 in]

0.00305 mm

/volt

92

0.8 mm

[0.031 in]

0.00305 mm

/volt

-19 2018 Center

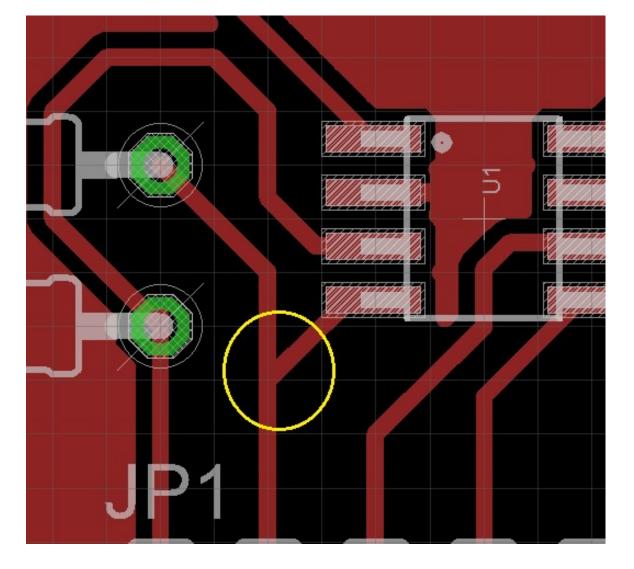

## **Acid Traps**

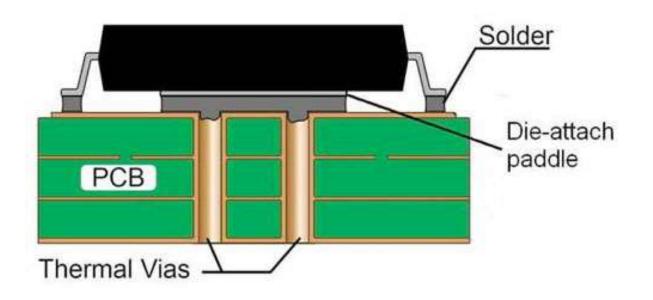

# Thermal Vias in Thermal Pad to Remove Heat

Datasheet or Mechanical or Thermal Analyzer Engineer

### Mechanical Issue – Vibration Design IPC-2221 Chapter 5

IPC-2221

level of vibration transmitted to the board. Particular attention should be given to printed boards subjected to random vibration.

The following criteria should be used as guidelines for determining if the level of vibration to which the boards will be subjected is a level which would require complex vibration analysis of the board:

- The random spectral density is at, or above,  $0.1G^2/Hz$  in the frequency range of 80 to 500 hertz or an unsupported board distance of greater than 76.2 mm.

- A sinusoidal vibration level at, or above, 3 Gs at a frequency of 80 to 500 Hz.

**5.3.2 Part Support** All parts weighing 5.0 gm, or more, per lead **shall** be supported by specified means (see 8.1.12), which will help ensure that their soldered joints and leads are not relied upon for mechanical strength.

The reliability of printed boards that will be subject to shock and vibration in service require consideration of the following criteria:

• The worst-case levels of shock and vibration environment for the entire structure in which the printed board assembly resides, and the ultimate level of this environment that is actually transmitted to the components on the board. (Particular attention should be given to equipment that will be subjected to random vibration.)

IPC the Institute for Interconnecting and Packaging Electronic Circuits

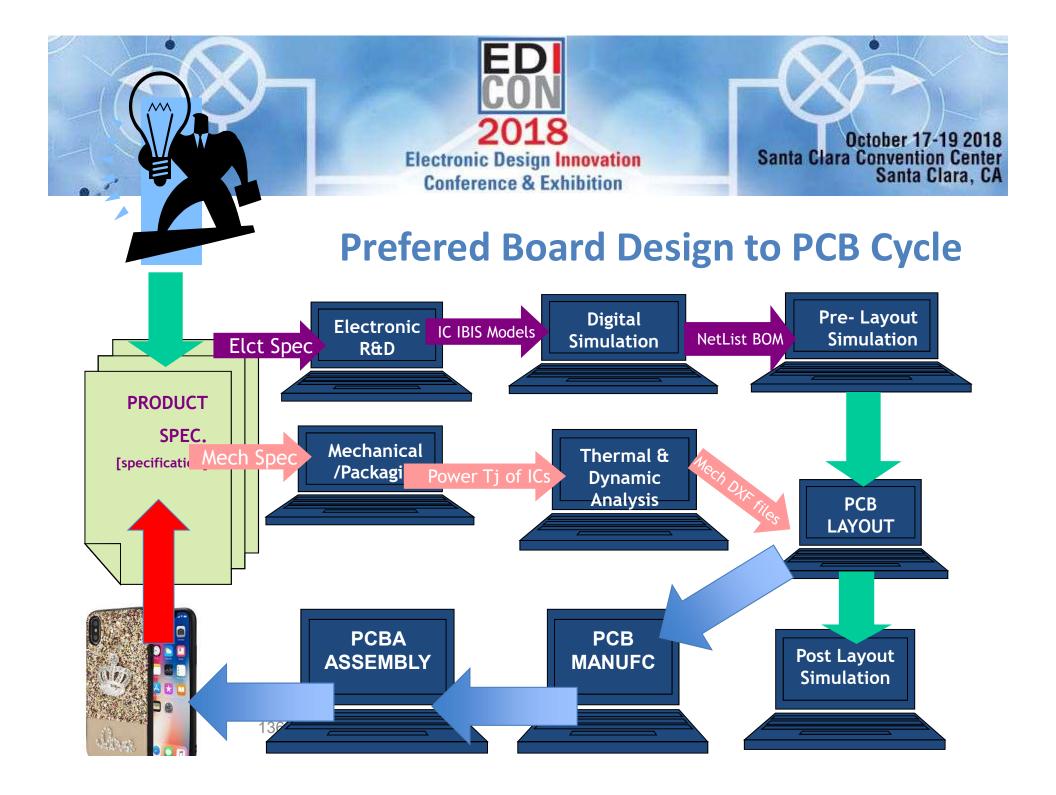

## Start with the End Choose the PCB Manufacturer before starting PCB Layout

To get the best Layers Construction for:

Impedance Control calculating with the **real Dielectric Constant** of the Laminates exist in **storage** Exact Dielectric Constant & Loss Tangent for each thickness of the Dielectric Core/Prepreg

Using the minimum TH Via's diameter to improve Power Integrity

Copper Balance to eliminate disconnections pins-pads due to Bow & Twist Effect

Shalom-Shlomi-Zigdon@iTech-iCollege.com

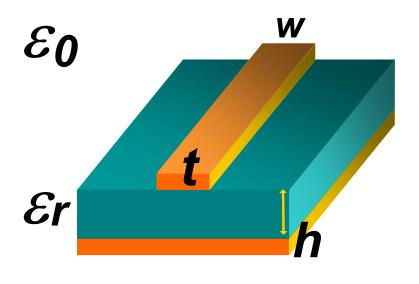

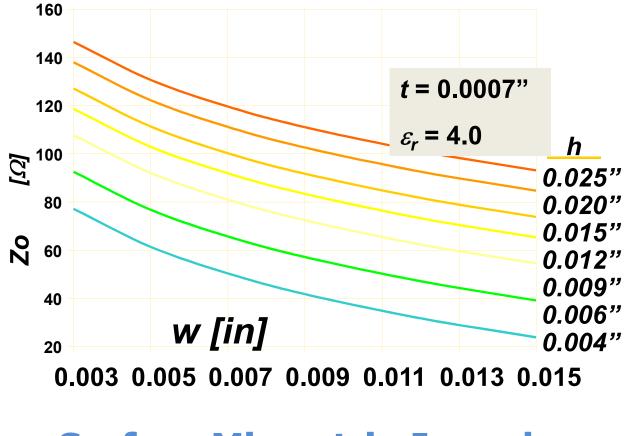

#### **The Finished Thickness influence the Impedance**

$$Z_0 = \frac{87}{\sqrt{\varepsilon_r + 1.41}} \ln\left(\frac{5.98h}{0.8w+t}\right) \left[\Omega\right]$$

**Surface Microstrip Impedance**

|             |                | Ø-                   |                 | Electronic Design Innovation<br>Conference & Exhibition | S              | anta Clara          | ctober 17-19 20<br>Convention Cer<br>Santa Clara, |  |

|-------------|----------------|----------------------|-----------------|---------------------------------------------------------|----------------|---------------------|---------------------------------------------------|--|

| <u>nick</u> |                |                      | er Proce        | ssing Exte                                              |                | -                   | l Thickne                                         |  |

| r           | Inte           | rnal La              | <u>yer Foil</u> | IPC-2151                                                | AILE           | After Plating       |                                                   |  |

|             | Copper<br>Foil | М                    | inimum          | PCB Cross Section<br>Before Etch                        | Copper<br>Foil | Mini                | imum                                              |  |

|             | 1/8 oz         | 3.5 μm               | 0.000138 in     | Resist Resist                                           | 1/8 oz         | 20 µm               | 0.000787                                          |  |

| Ī           | ¼ oz           | <mark>6.0 μ</mark> m | 0.000236 in     | Copper                                                  | 1⁄4 oz         | 20 µm               | 0.000787                                          |  |

|             | 3/8 oz         | 8.0 µm               | 0.000315 in     | Laminate                                                | 3/8 oz         | 25 μm               | 0.000984                                          |  |

|             | ½ 0Z           | 12.0 μm              | 0.000472 in     |                                                         | ½ oz           | <mark>33 μ</mark> m | 0.001299                                          |  |

|             | 1 oz           | 25.0 μm              | 0.000984 in     |                                                         | 1 oz           | 46 µm               | 0.001811                                          |  |

|             | 2 oz           | 56.0 μm              | 0.002205 in     | After Etch<br>Resist Resist                             | 2 oz           | 76 µm               | 0.002992                                          |  |

| Ī           | 3 oz           | 91.0 μm              | 0.003583 in     | Copper Copper                                           | 3 oz           | <b>107</b> μm       | 0.004213                                          |  |

| 1           | 4 oz           | 122.0 μm             | 0.004803 in     | Laminate                                                | 4 oz           | 137 μm              | 0.005394                                          |  |

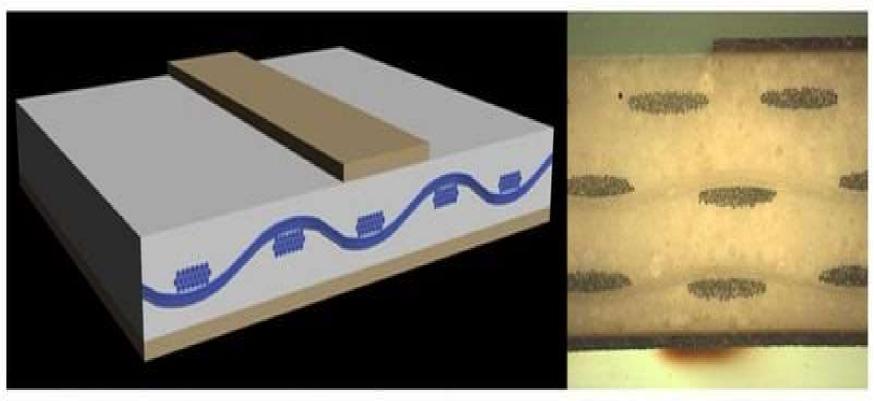

3D drawing of a microstrip transmission line

Cross-section of a microstrip

####

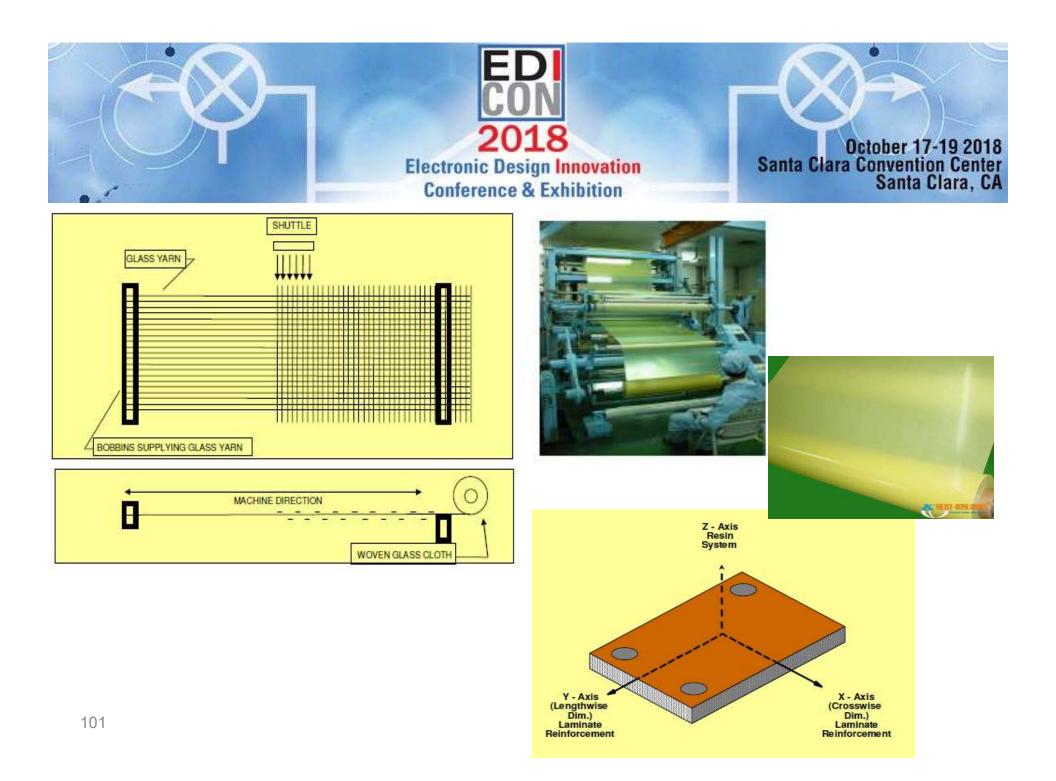

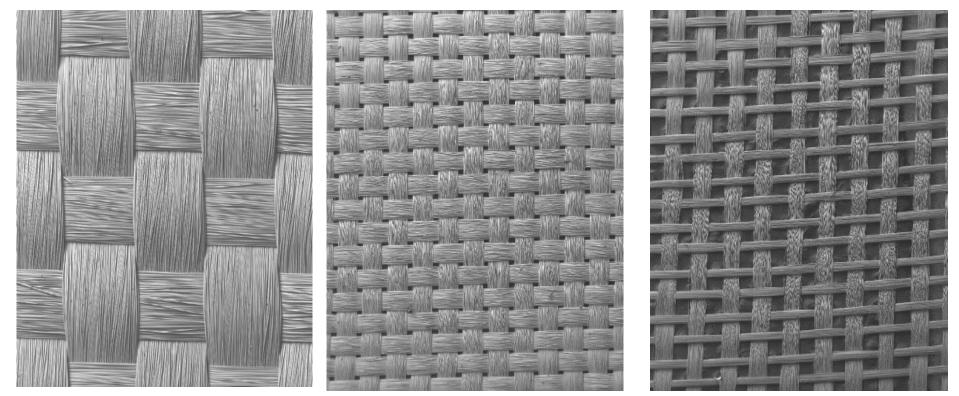

# **Fiber-glass Woven types**

## **Dielectric Material Selection**

The key parameters to consider :

- the dielectric constant Dk=εr

- the loss tangent Df [Dissipation Factor]

- the glass transition temperature (Tg)

- the fiber weave characteristics

- the dielectric breakdown voltage (DBV)

#### **Typical Dielectric Materials Used for PCB Design**

| Material Name            | Relative Dielectric<br>Constant | Loss Tangent | Highest Data Sheet<br>Frequency (GHz) |

|--------------------------|---------------------------------|--------------|---------------------------------------|

| Generic FR4              | 4.50                            | 0.015        | N/A                                   |

| Megtron 4                | 3.80                            | 0.005        | 1                                     |

| TU-872LK                 | 3.80                            | 0.009        | 10                                    |

| FR408HRIS                | 3.37                            | 0.0092       | 10                                    |

| EM-888                   | 3.80                            | 0.008        | 10                                    |

| EM-888K                  | 3.20                            | 0.006        | 10                                    |

| Nelco N4000-13           | 3.70                            | 0.008        | 10                                    |

| Nelco N4000-13 Si        | 3.30                            | 0.007        | 10                                    |

| Megtron 6                | 3.63                            | 0.004        | 12                                    |

| Rogers 4003C             | 3.38                            | 0.0027       | 10                                    |

| Rogers 4350B             | 3.48                            | 0.0037       | 10                                    |

| Taychon 100G             | 3.02                            | 0.0021       | 10                                    |

| Megtron 7 (Low Dk Glass) | 3.35                            | 0.002        | 12                                    |

| I-Speed                  | 3.63                            | 0.0071       | 10                                    |

| I-Speed IS               | 3.27                            | 0.0064       | 10                                    |

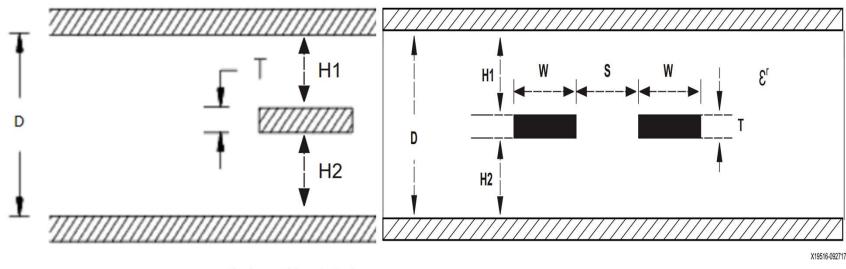

#### Example Stackup to Achieve 50 $\Omega$ Single-Ended Impedance

| Dielectric Material | ٤ <sub>r</sub> | Trace Thickness<br>(T) | W (mil) | D (H1+H2+T)<br>(mil) | Single-Ended Trace<br>Impedance (ohms) |

|---------------------|----------------|------------------------|---------|----------------------|----------------------------------------|

| Generic FR4         | 4.50           | 0.6                    | 3       | 8.6                  | ~50                                    |

| I-Speed IS          | 3.27           | 0.6                    | 3       | 7.1                  | ~50                                    |

#### Example Stackup to Achieve 100 $\Omega$ Differential Trace Impedance

| Material    | ٤ <sub>r</sub> | Trace Thickness<br>(T) | W (mil) | Spacing (S) | D (H1+H2+T)<br>(mil | Differential Trace<br>Impedance (ohms) |

|-------------|----------------|------------------------|---------|-------------|---------------------|----------------------------------------|

| Generic FR4 | 4.5            | 0.6                    | 3       | 10          | <mark>8.6</mark>    | ~100                                   |

| I-Speed IS  | 3.27           | 0.6                    | 3       | 10          | 7.1                 | ~100                                   |

Shalom-Shlomi-Zigdon(

Differential Edge-Coupled Centered Stripline

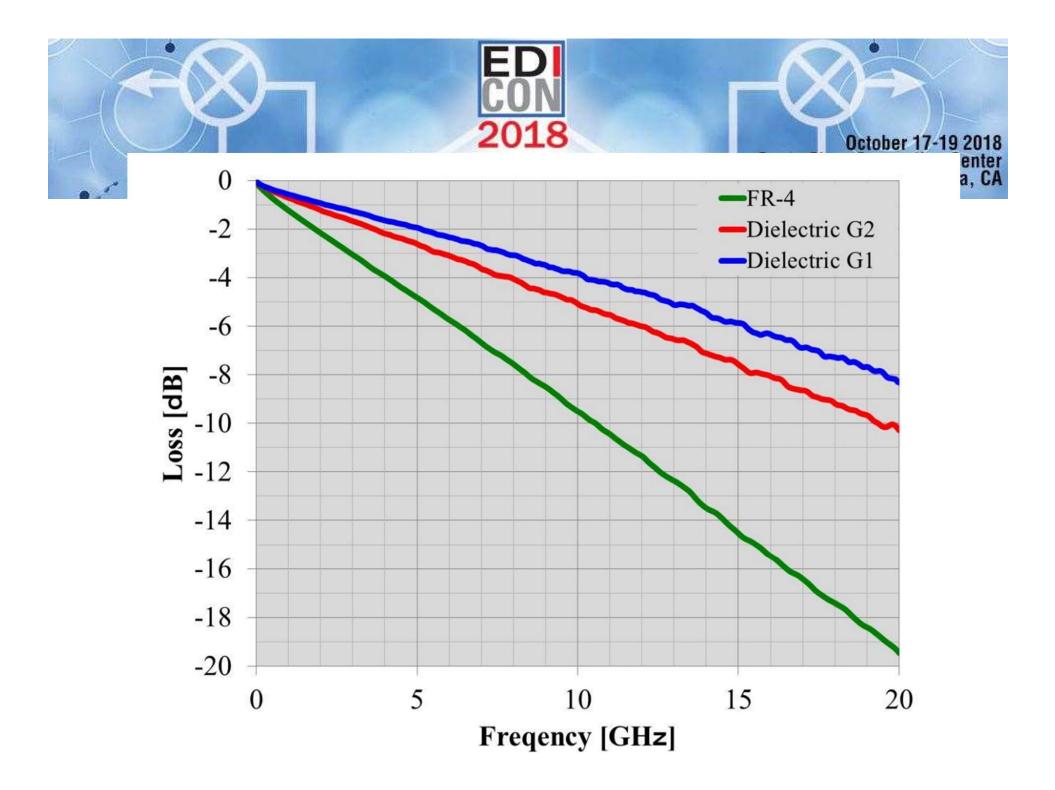

### Loss Tangent (Df)

a measure of the amount of RF energy absorbed by the laminate.

The loss tangent is a combination of the resin system has & the fiberglass cloth.

Similar to Dk, the loss tangent  $tan(\delta)$  or Df also varies with frequency and is dependent on the composition of the glass-to-resin ratio

Attenuation [dB/in] =  $2.3 \times f \times Df \times rsq \mathbf{E} r$

- f is the sine wave frequency in GHz

- Df is the loss tangent

- Er is the relative permittivity

## Picking a dielectric material with low Dk and low Df is recommended for the best signal integrity

## the **dielectric loss** is the **dominant** loss mechanism to be concerned with when designing a PCB for high-speed applications.

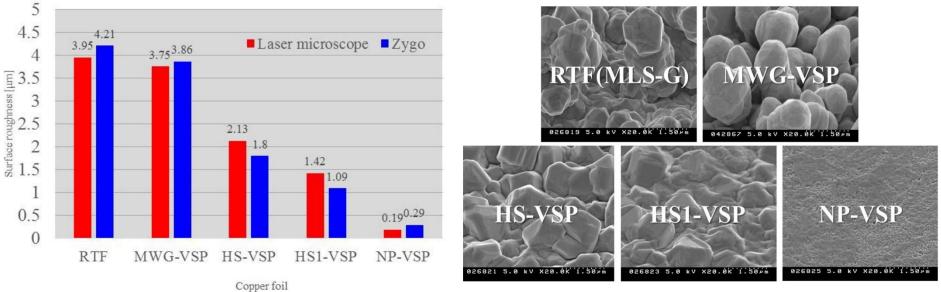

# different Roughness

# Roughening treatment is applied to surface of copper foils by depositing copper nodules

## Tg Glass Transition Temperature

the **temperature** at which a **resin's CTE** [coefficient of thermal expansion] changes to a much larger value than it has at lower temperatures.

The Z-Axis CTE is 4 times the x/y-Axis CTE

PCB with 14+ Layers >>> De-Lamination [popcorn]

| Electronic Design Innovation<br>Conference & Exhibition | October 17-19 201<br>Santa Clara Convention Cente<br>Santa Clara, C |

|---------------------------------------------------------|---------------------------------------------------------------------|

|                                                         | October 17-19 20<br>Santa Clara Convention Cen<br>Santa Clara,      |

|                                                                     | Material                   |                                       |                                           |                                    |                        |                  |

|---------------------------------------------------------------------|----------------------------|---------------------------------------|-------------------------------------------|------------------------------------|------------------------|------------------|

| IPC-2221 Environmental Property                                     | FR-4<br>(Epoxy<br>E-glass) | Multifunctional<br>Epoxy<br>(E-glass) | High<br>Performance<br>Epoxy<br>(E-glass) | Bismalaimide<br>Triazine/<br>Epoxy | Polyimide<br>(E-glass) | Cyanate<br>Ester |

| Thermal Expansion<br>xy-plane (ppm/°C)                              | 16 - 19                    | 14 - 18                               | 14 - 18                                   | ~ 15                               | 8 - 18                 | ~ 15             |

| Thermal Expansion z-axis below T <sub>g</sub> <sup>3</sup> (ppm/°C) | 50 - 85                    | 44 - 80                               | ~44                                       | ~70                                | 35 - 70                | 81               |

| Glass Transition<br>Temp. T <sub>g</sub> (°C)                       | 110 - 140                  | 130 -160                              | 165 - 190                                 | 175 - 200                          | 220 - 280              | 180 - 260        |

| Flexural Modulus<br>(x 10 <sup>10</sup> Pa)                         |                            |                                       |                                           |                                    |                        |                  |

| Fill <sup>1</sup><br>Warp <sup>2</sup>                              | 1.86<br>1.20               | 1.86<br>2.07                          | 1.93<br>2.20                              | 2.07<br>2.41                       | 2.69<br>2.89           | 2.07<br>2.20     |

| Tensile Strength<br>(x 10 <sup>8</sup> Pa)                          |                            |                                       |                                           |                                    |                        |                  |

| Fill <sup>1</sup><br>Warp <sup>2</sup>                              | 4.13<br>4.82               | 4.13<br>4.48                          | 4.13<br>5.24                              | 3.93<br>4.27                       | 4.82<br>5.51           | 3.45<br>4.13     |

<sup>1</sup> Fill - yarns that are woven in a crosswise direction of the fabric.

<sup>2</sup> Warp (cloth) - yarns that are woven in the lengthwise direction of the fabric.

<sup>3</sup> Z-axis expansion above T<sub>g</sub> can be as much as four times greater. For FR-4 it is 240-390 ppm. Contact supplier for specific values of the other materials.

Shalom-Shlomi-Zigdon@iTech-iCollege.com

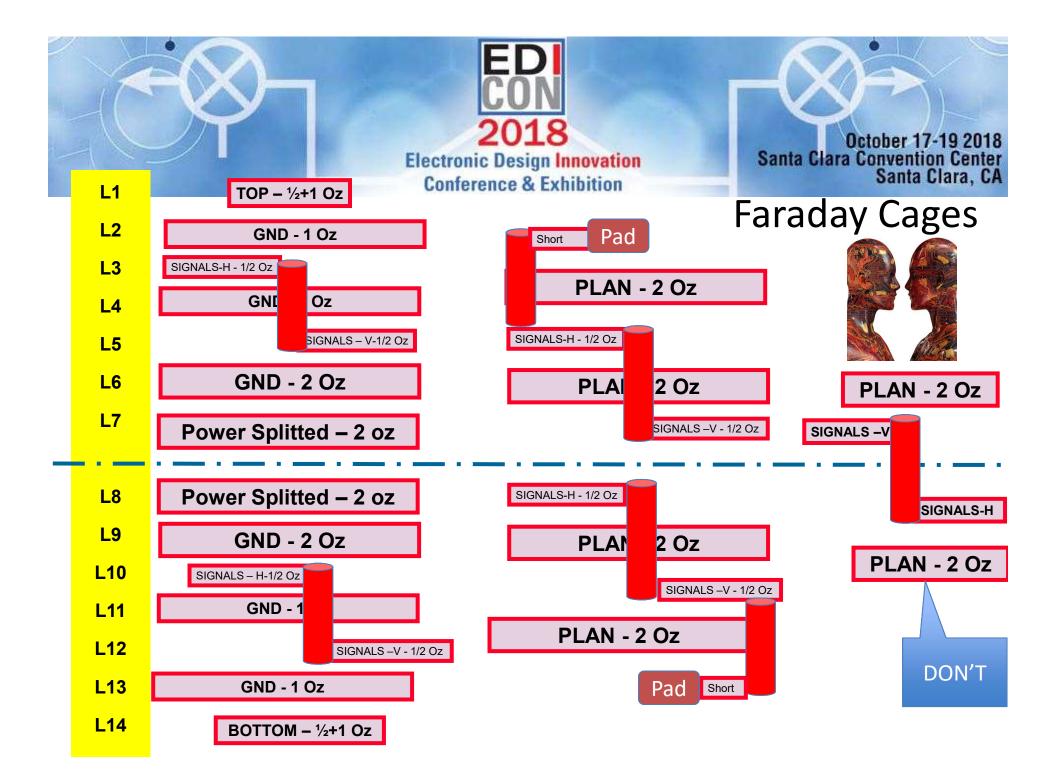

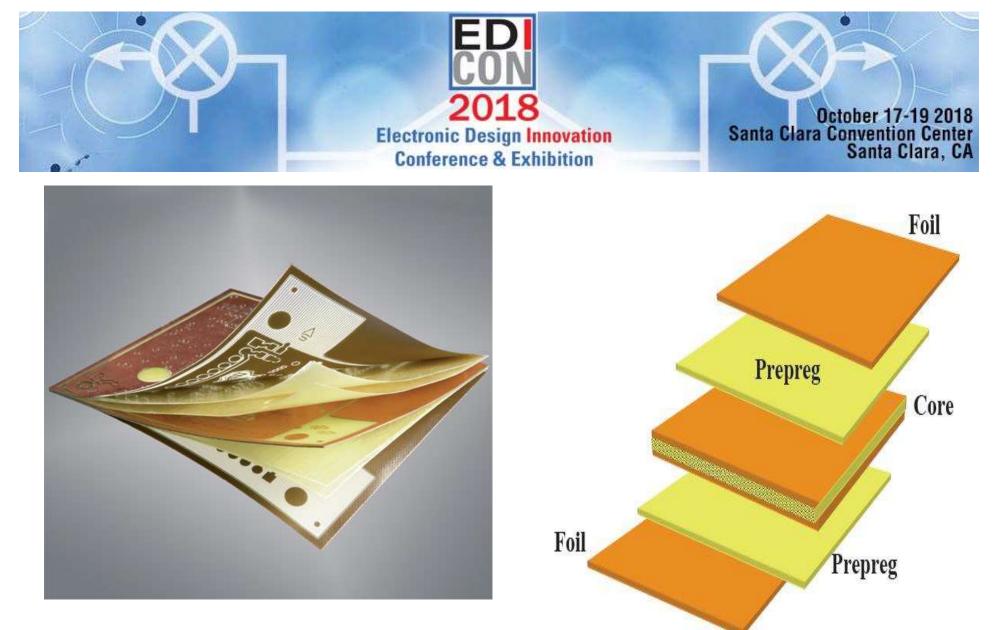

#### Layers Construction

- Manufacturer recommendation PCB Layers Construction is very real Design

- Impedance calculation calculated with the real PCB Materials in storage

- Exact Dielectric Constant, Loss Tangent for each thickness of the Dielectric Cores/Prepreg

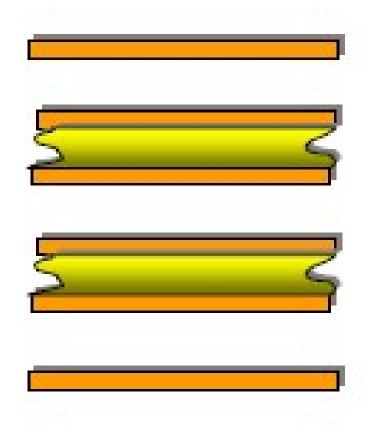

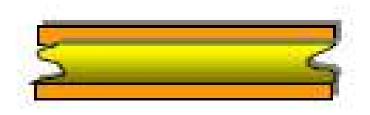

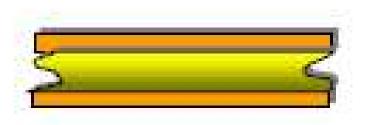

#### **Foil vs Core Construction**

#### **Foil Construction**

#### **Core Construction**

## Conclusion – Start with the End Get advice from your Manufacturer before PCB Layout

#### **Embedded Resistors use as Terminations**

Shalom-Shlomi-Zigdon@iTech-iCollege.com

# preferred for this PCB

Signal Integrity

VS.

**Power Integrity**

#### Conflicts

**Diameter of Vias**

VS.

#### Larger

minimize Via Inductive

reduce Power planes self Inductance

Smaller

# PCB Layout Design for EMC Compliance to reduce the cost and the time for EMC requirements [Mil-Std-461, FCC, EN/CE Directive]

## **Interference Modes in electronics**

- 1. Intra System-Inside the unit

- 2. Inter System to and from the environment

- Sources of High Frequency radiation:

- Digital electronics, especially clocks

- local oscillators of receivers

- spurious emissions from transmitters

- switching operations

- switching Mode Power supplies-SMPS

- High frequency radiating elements

- PCB Traces

- Return Current Path Loops

- Cables

- Antennas

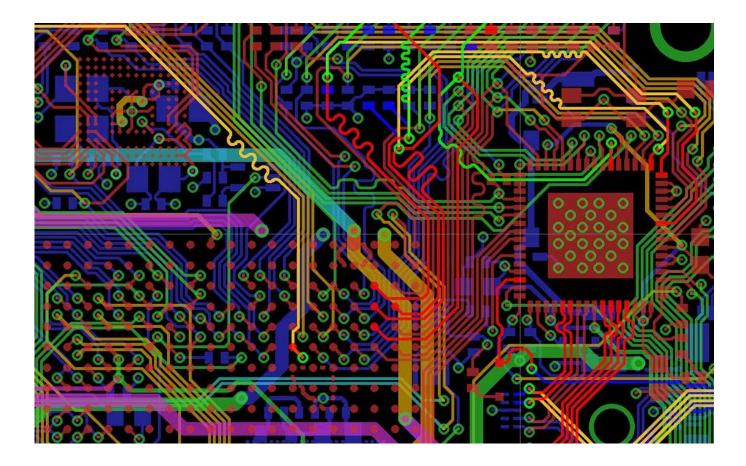

# **EMI Main Consideration**

# PCB Layout

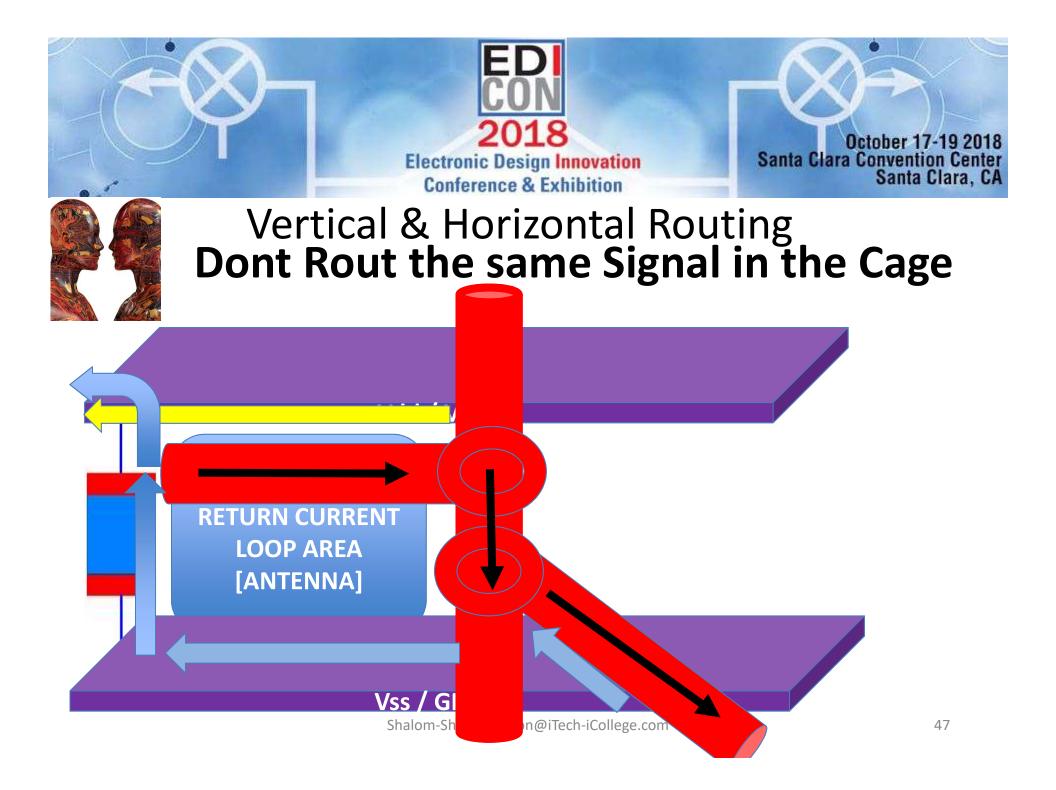

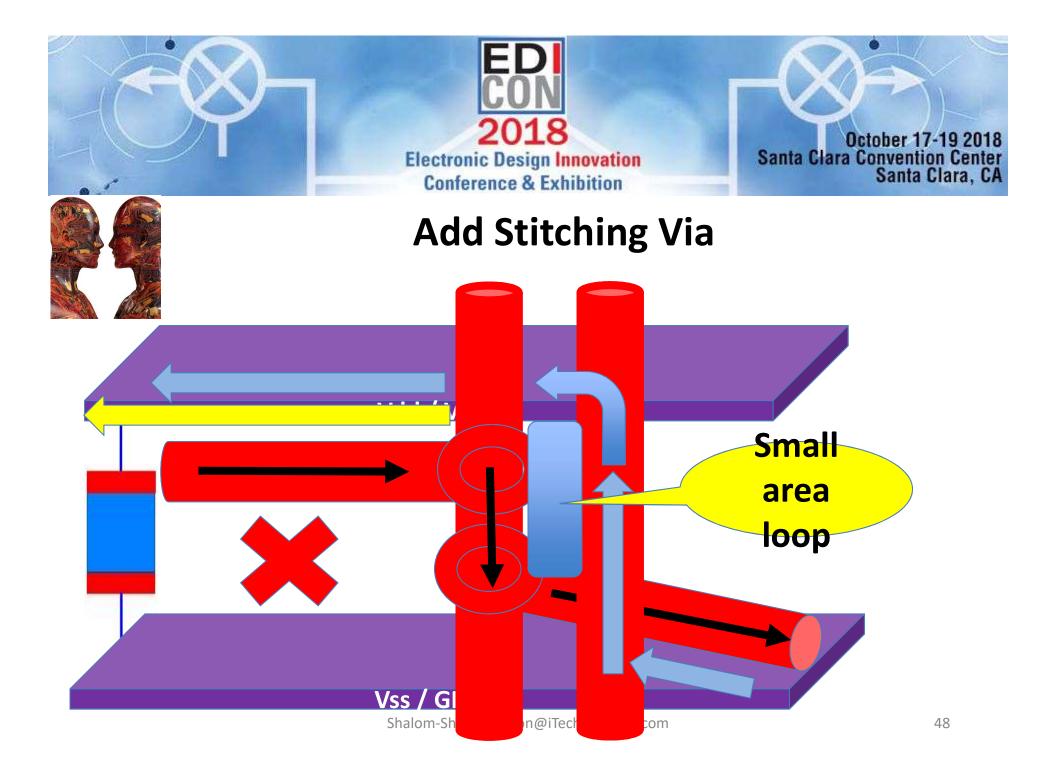

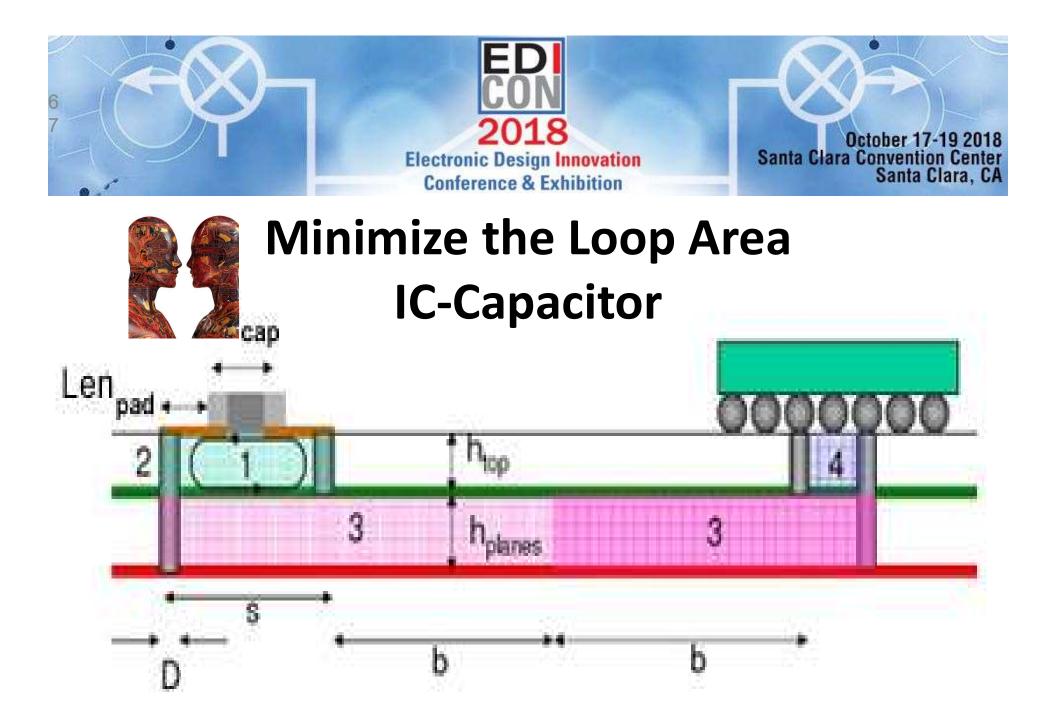

- 1. Signal + Current Return Loop Area

- 2. High Current Loop Area

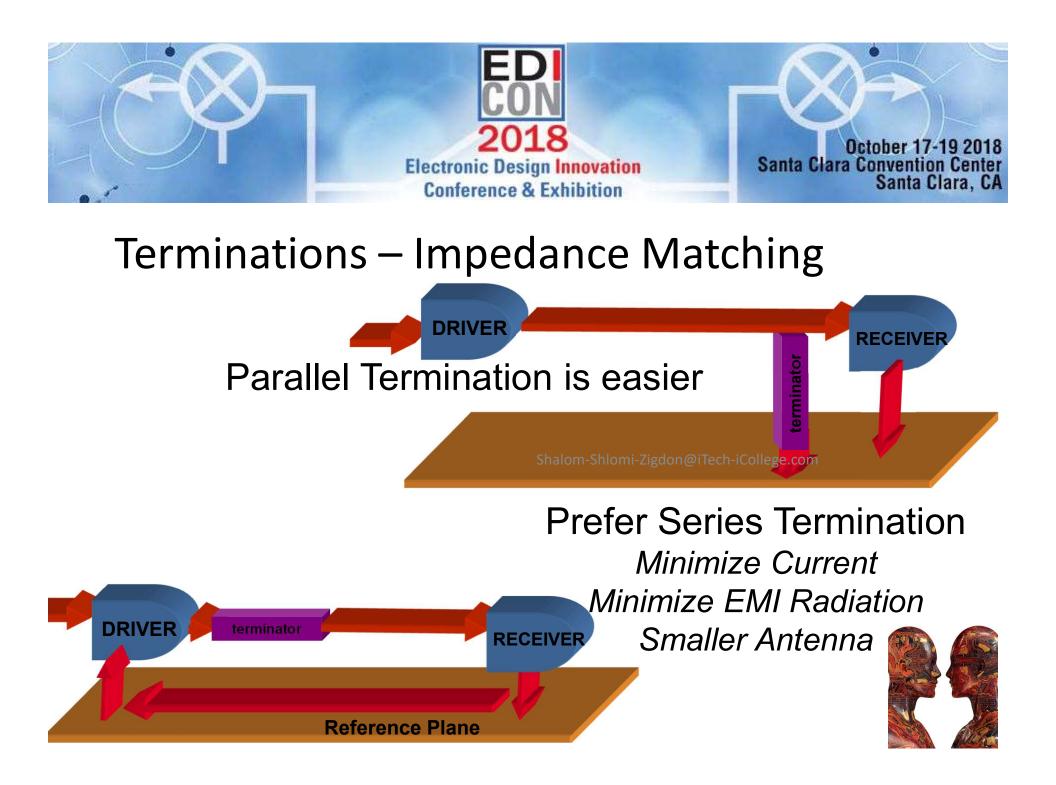

- 3. Impedance Control

- 4. Signal Termination

- 5. Decoupling/Bypassing Capacitor

- 6. Power Distribution

- 7. Grounding

- 8. Surge Suppression

System Level

- 1. Filtering

- 2. Cabling

- 3. Shielding

- 4. Bonding

## **Placement for EMC Control**

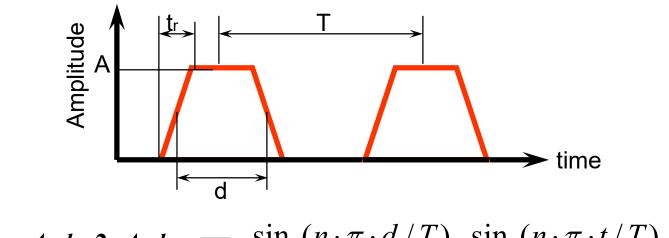

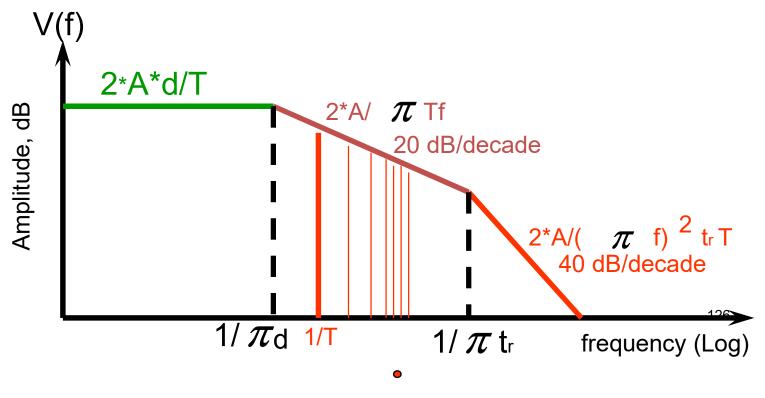

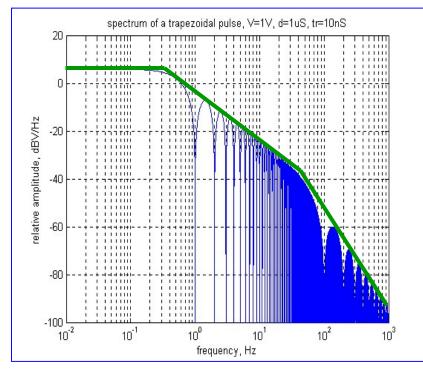

### **Spectrum of a Clock Pulse Train**

$$v(f) = \frac{A \cdot d}{T} + \frac{2 \cdot A \cdot d}{T} \star \sum_{n=1,2,3} \frac{\sin(n \cdot \pi \cdot d/T)}{n \cdot \pi \cdot d/T} \cdot \frac{\sin(n \cdot \pi \cdot t/T)}{n \cdot \pi \cdot t/T}$$

## Fourier series of discrete frequencies

125

#### **Spectrum of a Clock Pulse Train**

מבוא לתא"מ

- Pulse spectra can be described by 3 segments in the Log Amplitude and Frequency plane:

- Low frequency, up to f<sub>1</sub>, determined by d

- Medium frequency, up to  $f_2$ , determined by  $t_r$

- High frequency, above f2

- Clock spectra contains clock harmonics

### **Pulse Spectra**

Shalom-Shlomi-Zigdon@iTech-iCollege.com

#### Wide Conductor Advantages

#### Greater Characteristic Capacitance to GND Plane

- Minimize Characteristic Impedance

- Minimize self inductance of the conductor

- Minimize EMI radiation

Minimize Crosstalk by mutual Inductance between conductors

Minimize conductor Resistance [a must for 10Gbps]

Noisy Circuit place in the middle of PCB noisy/susceptible components Away from any I/O Connectors and Power Supply Circuits.

uP, uC, FPGA Oscillators Crystal Clock Dividers Data & Address Busses SWPS Switching Mode Power Supply Transformators, Common Mode Chockes Non-grounded Heatsinks

Away from Sensitive Analog Circuits [microvolt – millivolt inputs from Sensors] OP-AMP [operational amplifiers]

130

- 1. I/O Signals are Paths of EMI off The PCB

- 2. Avoid routing High Speed Signals beneath I/O Components

- 3. Ground any Heatsink to prevent Radiation of Coupled Fields

#### **Summary of Control of Radiation Traces**

- Keep Area of radiating antenna small

- Place differential wires together, and twist.

- place wires close to ground plane.

- keep lengths short.

- Limit High Frequency Noise Voltage and Current

- Use low current devices

- Long rise/fall times.

- low pass filtering.

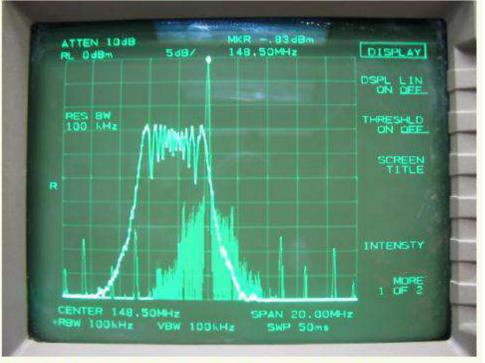

#### **Spread Spectrum Clock Generator**

#### Measured Results of the SSCG

•F<sub>m</sub> = 100 KHz.

•F<sub>dev</sub> = 3.0 %.

•PPR >13 dB.

•F<sub>pll</sub> = 5.5\*F<sub>ref</sub>

Spectrum analyzer view with and without SSCG:

133

## **Chassis Guard for ESD**

134

## PCB Generations – SI/PI/EMC Perspective

ED

| -1 | Gen. | Situation                     | Conductor                                      | Results                                                                |

|----|------|-------------------------------|------------------------------------------------|------------------------------------------------------------------------|

|    | 1    | DC of DC                      | Short between ptp                              | Current/Voltage                                                        |

|    | 2    | AC of DC                      | Self-Inductance                                | EMI & Crosstalk                                                        |

|    | 3    | BGA Packages                  | Power Planes Inductance                        | Ground/Power Bounce<br>SSN, SSO                                        |

|    | 4    | Hi-Speed                      | Transmission Line<br>Impedance Control         | Signal = E.M. Wave<br>Reflection<br>Overshoot/Undershoot<br>Distortion |

|    | 5    | Higher Speed<br>Lossy line #1 | Skin Effect                                    | Conductor Resistance<br>Varies with Frequency<br>Attenuation           |

|    | 6    | Lossy line #2                 | Conductor Environment<br>= Dielectric Material | Dielectric Losses<br>Attenuation                                       |

|    | 7    | Multi-Giga F                  | Differential Pair                              | Via Effects                                                            |

Analog Engineers know the world is Analog RF Engineers know the world is Analog

#### **Hi Digital Engineer**

The world is Analog

Any "Digital world" is an illusion

The Schema is more "Concept" than "Fact"

# The real world is the **PCB It is not a Paradise at all**

#### **Right the First Time?**

## As a **Quality management concept** that *defect prevention* is more advantageous and cost effective than *defect detection* and associated rework.

It can be achieved

## I hope I helped you a bit Thank you very much

#### For Slides ask me on Email or on Website

Shalom-Shlomi-Zigdon@iTech-iCollege.com

## Fourier Transform